Xilinx可编程逻辑器件设计与开发(基础篇)连载34:Spartan

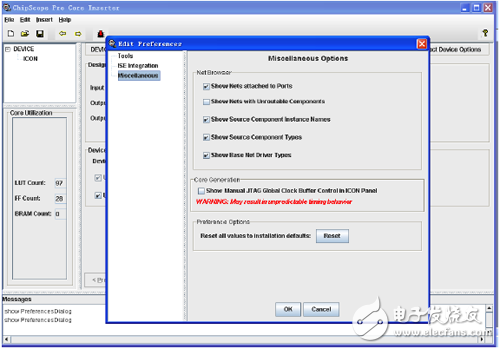

打开【Edit】菜单→【Preferences】属性,弹出【Edit Preferences】属性编辑对话窗,如图9-31所示。

使能JTAG全局时钟缓冲器控制:在【Miscellaneous】选项卡里,【Show Manual JTAG Global Clock Buffer Control in ICON Panel】复选框选中。

禁止JTAG时钟上的BUFG:【Put JTAG Clock on a Global Clock Buffer】复选框不选中。

图9-31 【Edit Preferences】界面

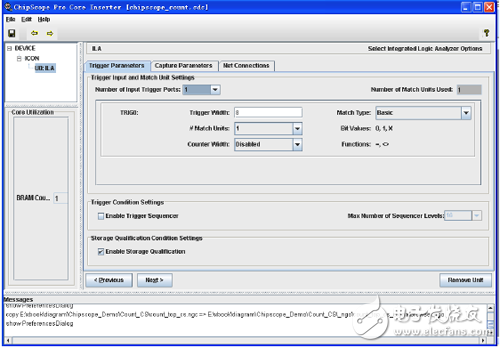

(3) 在图9-30中单击【New ILA Unit】,弹出ILA触发选项和参数设置界面,如图9-32所示。

图9-32 ILA触发选项和参数设置界面

Trigger Parameters选项卡:

Trigger Input and Match Unit Settings选项组:

【Number of Input Trigger Ports】下拉列表框:选择ILA核输入触发端口数目,ILA核最多支持16个输入触发端口。每个触发端口的参数在下方列出,包括触发宽度、触发匹配条件判断类型和数目。

TRIGn选项组:

【Trigger Width】编辑框:触发端口由一条或者多条信号线组成,信号线的总数成为触发宽度,最大为256。

【# Match Unit】下拉列表框:触发比较匹配单元是个比较器,和触发端口相连,用于检测触发端口是否满足设定的条件。每个触发端口可以有1~16个触发匹配单元。触发匹配设置单元设置的越多,触发事件就越灵活,但是要占用更多的内部资源。在满足条件的情况下,尽量减少触发匹配单元的数量。

【MatchType】下拉列表框:请参见表9-1。

【Count Width】下拉列表框:匹配单元计数器宽度,用于选择满足匹配条件的次数,最大32位。

Trigger Condition Settings选项组

【Enable trigger condition sequencer】复选框:设臵是否使能触发队列器和队列器深度。触发序列是为了增加触发的复杂性,使触发的条件更加特殊,我们可以把若干个状态组合起来形成触发条件,这样就能更好的使用有限的资源存储有用的数据。

【Max Number of Sequencer levels】下拉列表框:设臵最大的触发条件序列级数。

Storage qualification condition Settings选项组

【Enable Storage Qualification】复选框:存储器限制条件。请参考9.2.2小节中的相关内容。

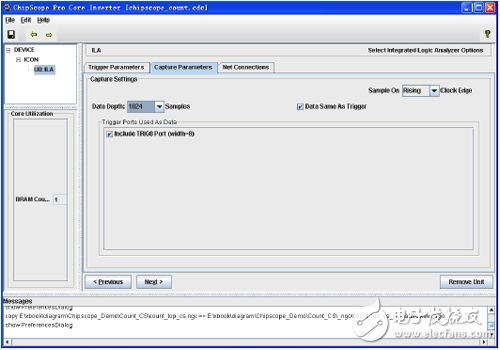

Captures Parameters选项卡:采样参数选项卡(参见图9-33)。

图9-33 【Captures Parameters】参数设置界面

【Sample On】下拉选择框:设臵在时钟的上升沿或者下降沿采集数据。

【Data Depth】下拉选择框:设臵ILA核存储的最大数据采样个数。

【Data Same as Trigger】复选框:设臵ILA触发端口和数据采集端口是否相同。请参考9.2.2小节中的相关内容。

Trigger Port Used As Data选项组:

如果选中了【Data Same As Trigger】复选框,那么在数据选项的每个TRIGn端口前都会出现一个【Include TRIGn Port】复选框,选中该选项,表明数据和触发端口合并。

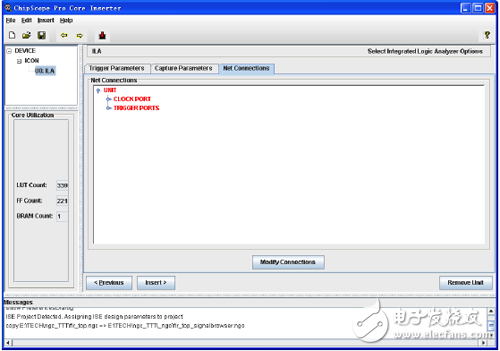

Net connections选项卡(参见图9-34)。

图9-34 【Net connections】网络连接界面

Net Connections选项组:用于将集成逻辑分析仪ILA核的输入信号与设计中的网线连接起来。如果触发和数据信号分离,那么必须指定数据、时钟和触发端口。双击【CLOCK PORT】或者单击【CLOCK PORT】左边的加号(+)。如果还没连接,该选项显示为红色。如图9-34所示,包括【CLOCK PORT】和【TRIGGER PORTS】两组端口的连接。

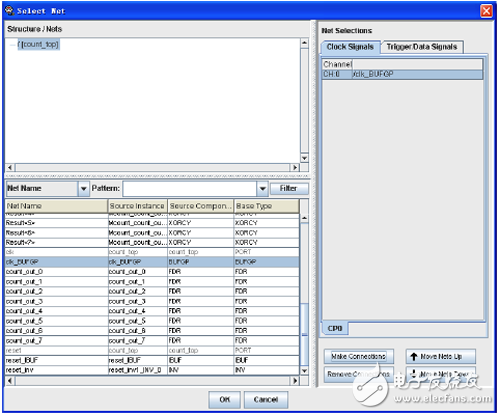

【Modify Connections】按钮:单击该按钮弹出【Select Net】对话框,对话框很容易地将ILA核工作时钟、触发信号、数据信号与设计中的网线连接起来,如图9-35所示。

【Structure/Nets】窗格:列出设计的层次结构。

【Net Name】:EDIF网表中的网络名,由于重命名或者综合中的优化原因,可能和HDL中的源码名字不一样。

【Source Instance】:当前综合结果中较低层次的元件例化名称。

【Source Component】:【Source Instance】选项中描述的组件。

【Base Type】:最底层的组件类型,基本类型为原语(primitive)或黑盒子。

【Pattern】编辑框和【Filter】按钮:通过这两个选项,可以有选择地显示设计中可用于ChipScope的网线。

【Remove Connections】按钮:删除当前的连接。

【Move Nets Up】按钮:向上移动连接的位臵。

【Move Nets Down】按钮:向下移动连接的位臵。

【Make Connections】按钮:连接所选择的网络节点和ChipScope内核。

图9-35 【Select Net】界面

在【Structure/Nets】中,选择想要连接到ChipScope核的网络节点(可以配合Shift/Ctrl键,选择多个网线)。在【Net Selections】中选择【Clock Signals】、【Tr

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)