Nexys3学习手记5:流水灯在线运行

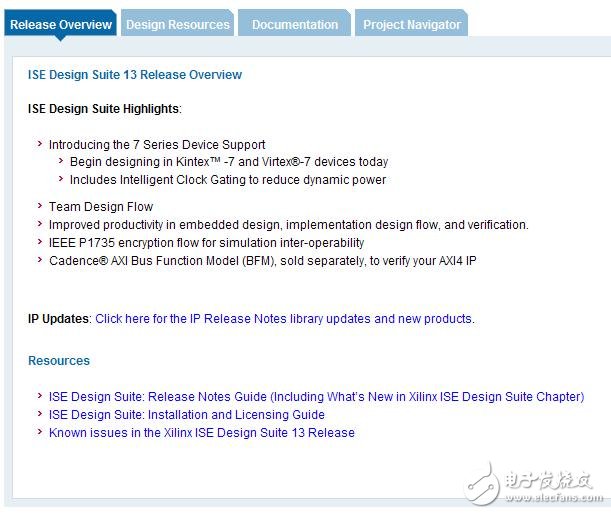

在进行第一个工程实例前,顺便提一下设计工具相关资源的获取。从特权同学接触的几家FPGA开发工具来看,Xilinx在这方面做得应该算是最人性化的了,其设计资源可谓唾手可得。如图1所示,当我们开启ISE软件后,主窗口便会显示这样一个带有介绍和引导链接的页面。这里我们主要提一下它的DocumentaTIon。

图1 ISE设计资源引导界面

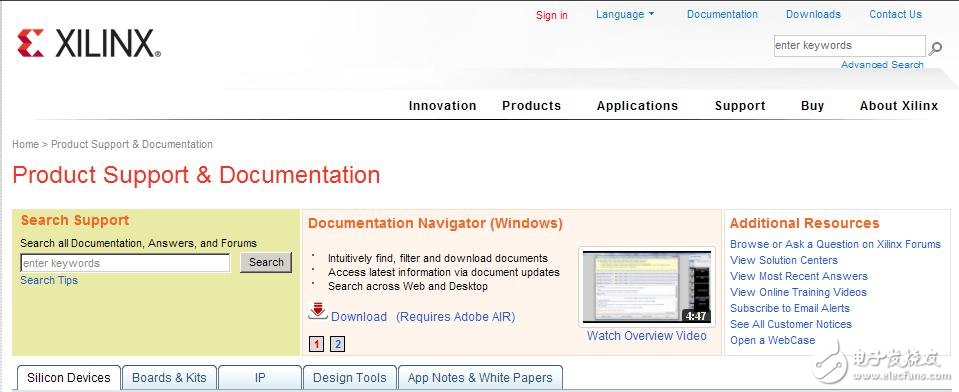

点开DocumentaTIon,如图2所示,其实是直接打开了Xilinx的一个客户端小工具DocumentaTIon Navigator(简称DocNav)的下载页面。这是一款不错的Xilinx设计文档在线浏览工具,非常推荐各位下载并安装。

图2 DocumentaTIon页面

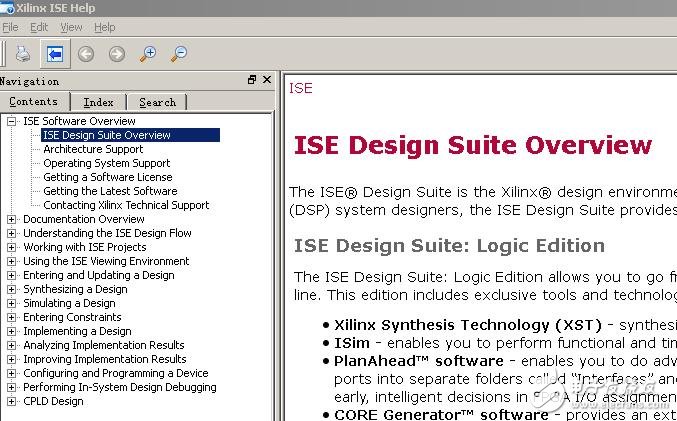

如图3所示,打开DocNav软件的首页,可以看到各类开发相关的归类文档,这个小工具让Xilinx的各类文档一目了然,极大的方便了设计者对文档资源的索取和阅读。这么大的一个文档资源库,恐怕花个一年半载的都未必能够通读一遍,实际上压根个也没有这个必要。一般来说,建议设计者对这些文档的基本用处有所了解即可,而在遇到一些设计小问题的时候脑子里能够灵光一现,想起来大概哪个文档里会有解决问题的办法,而后再过来翻看也就足够了。 图3 D

ocNav首页

再说每个软件都有Help,ISE中点开菜单栏的HelpàHelp Topics…,便如图4所示。记得特权同学大三那年一个被认为牛的不行的留过洋的微波课老师第一次和我们提Project,还让我们用Matlab画smith圆图,那时对专业英文一知半解的我们才发现原来Help里面要啥有啥,真可谓大百科全书。所以捏,同学们都要好好利用Help这玩意,不懂就问,最简单快捷的问法就是Search。

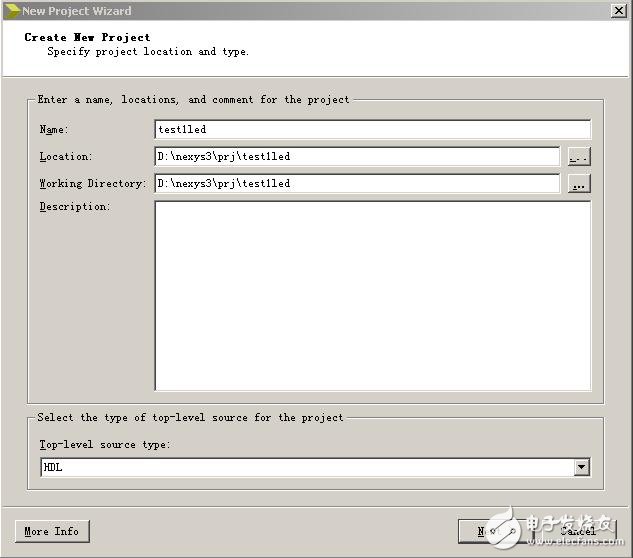

图5 工程名与存储设置

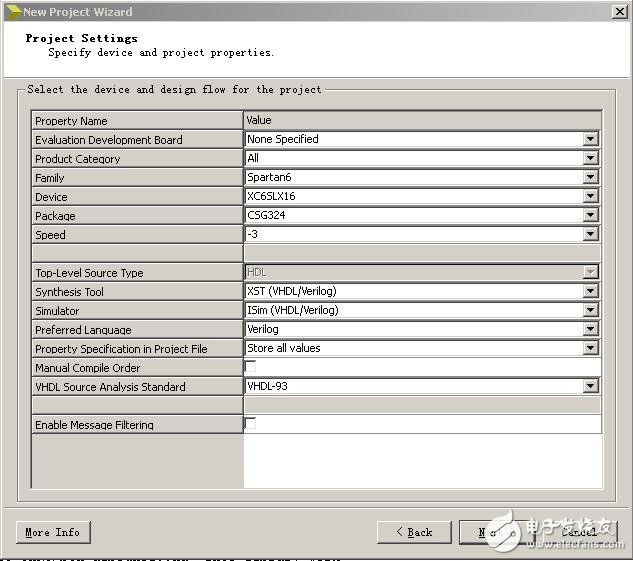

器件与工程属性设置如图6所示。设置完毕再Next便Finish。

图6 器件与工程属性设置

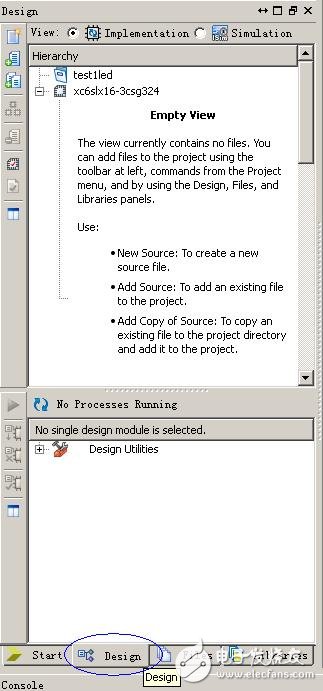

此时我们看工具左侧窗口,选中Design便如图7所示。Hierarchy下只有工程名和相应器件显示,可谓设计文件一片空白,咱要来此拓荒了。首先,我们需要添加源代码文件到工程中。

图7 Design窗口

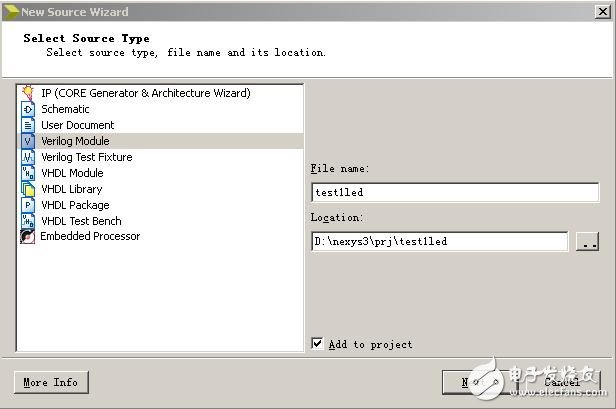

在Hierarchy窗口的空白处右键点击New Source…,如图8所示。这里可以选择新建各类源文件,包括IP核、基于处理器的系统、verilog或VHDL源文件以及测试脚本等等。我们需要新建一个verilog源代码文件,所以选择Verilog Module,给模块命名,通常顶层代码源文件名建议和工程名一致,免得后面一串麻烦事。

图8 新建源文件

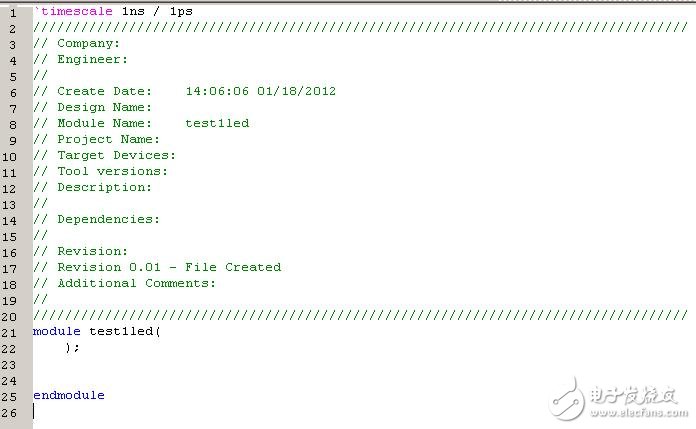

新建的源代码.v文件会自动添加到Hierarchy下,并且直接在主窗口中打开源文件如图9所示。

图9 源代码文件 此时需要编写一段流水灯测试代码,如下所示:module test1led( clk,rst_n, led ); input clk; //100MHzinput rst_n; //低电平复位信号 output[7:0] led; //分频信号,连接到蜂鸣器 //---------------------------------------------------reg[2:0] cnt; //分频计数器 always @ (posedge clk or negedge rst_n)//异步复位 if(!rst_n) cnt <= 23'd0; else cnt <= cnt+1'b1; //寄存器cnt循环计数 //----------------------------------------------------reg[7:0] ledr; //LED流水灯 always @ (posedge clk or negedge rst_n) if(!rst_n) ledr <= 8'd1; else if(cnt == 23'h7fffff) ledr <= {ledr[6:0],ledr[7]};//大约每80ms让led左移一次 assign led = ledr; endmodule 接下来需要对管脚进行分配,如图10所示,Hierarchy中需要先选中顶层代码文件testled.v,然后双击Processes下的User ConstraintsàI/O Pin Planning(PlanAhead) – Post-synthesis(或者I/O Pi

- Nexys3学习手记3:硬件外设走马观花(02-11)

- Nexys3学习手记7:MicroBlaze小试牛刀(02-11)

- Nexys3学习手记6:ClockingWizard探秘(02-11)

- Nexys3学习手记8:FT232之高速UART(02-11)

- Nexys3学习手记2:建立自己的开发环境(02-11)

- Xilinx Kintex UltraScale 一半尺寸的 PCI Express 平台 (HTG-K816)(06-15)