Nexys3学习手记8:FT232之高速UART

继续上一节的工程,这里要接着在XPS上扩展一个UART外设,配合板载的USB2UART芯片FT232R做个高速串口传输测试。

首先打开上一个ISE工程,然后双击顶层模块下的mycpu模块即可开启硬件开发平台XPS,如图1所示。

图1 点击进入XPS

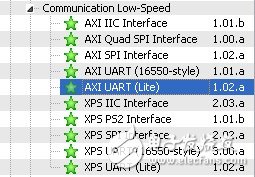

传说中XPS上提供了两个AXI总线对应的UART外设IP核,如图2所示,即UART 16550-style和UART-Lite。本节要添加的名为UART-Lite的外设,故名思意便是精简的小身板UART外设,几番接触下来,果然如此,对于复杂的UART使用这个Lite版还确实难堪大任,不过对于我们的实验学习还是多多益善,简单才容易玩转嘛,哈哈。

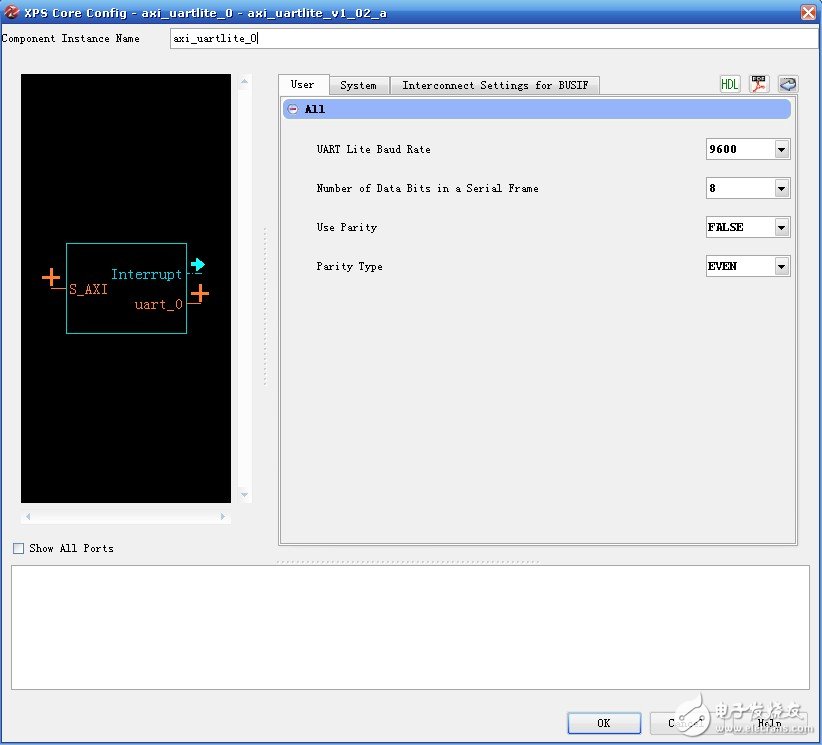

图3 UART-Lite外设配置页面

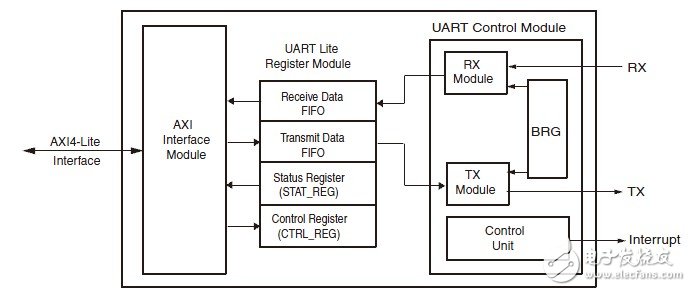

点击图3右上角的pdf小图标便可查看此外设的说明文档axi_uartlite_ds741.pdf。如图4所示,UART-Lite的功能框图中示意改外设包含了4个最基本的软件可访问的寄存器,即数据接收寄存器(Receive Data FIFO)、数据发送寄存器(Transmit Data FIFO)、状态寄存器(Status Register)和控制寄存器(Control Register)。

图4 UART-Lite功能框图

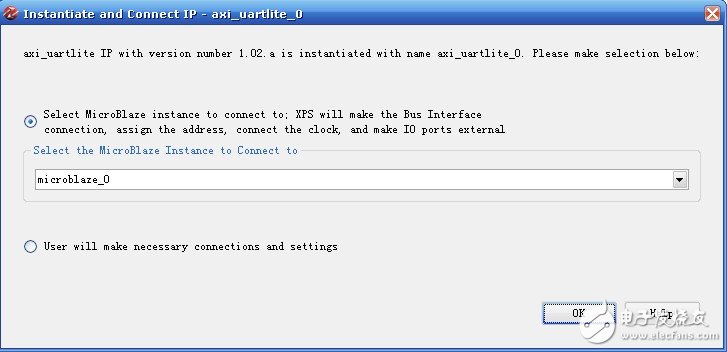

在完成UART-Lite的配置后,点击OK,便会弹出如图5所示的串口。采用默认设置,意为UART-Lite外设的AXI总线接口能够自动和系统的MicroBlaze处理器上的片内AXI总线接口相匹配。

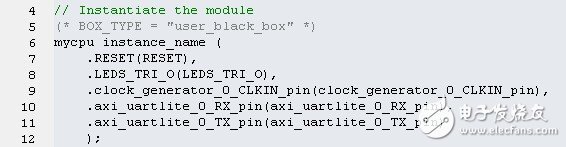

图6 系统例化模板 重新编辑并例化顶层文件,修改后的顶层代码如下:module testled( clk,rst_n, led, uart_rx,uart_tx ); input clk; //100MHzinput rst_n; //低电平复位信号 output[7:0] led; //连接到LED指示灯 input uart_rx; //UART数据接收output uart_tx;//UART数据发送 wire clk_100m; //clocking输出100MHzwire clk_50m; //clocking输出50MHzwire clk_25m; //clocking输出25MHzwire clk_12m5; //clocking输出12.5MHzwire clk_locked; //clocking输出完成标志位 //---------------------------------------------------//IP核Clocking Wizard例化//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG myclocking uut_myclocking (// Clock in ports .CLK_IN1(clk), // IN // Clock out ports .CLK_OUT1(clk_100m), // OUT .CLK_OUT2(clk_50m), // OUT .CLK_OUT3(clk_25m), // OUT .CLK_OUT4(clk_12m5), // OUT // Status and control signals .RESET(!rst_n),// IN .LOCKED(clk_locked)); // OUT// INST_TAG_END ------ End INSTANTIATION Template --------- //---------------------------------------------------// 例化mysoc系统(* BOX_TYPE = "user_black_box" *)mysoc uut_mysoc ( .RESET(rst_n), .LEDS_TRI_O(led), .clock_generator_0_CLKIN_pin(clk_100m), .axi_uartlite_0_RX_pin(uart_rx), .axi_uartlite_0_TX_pin(uart_tx) ); endmodule 对顶层新添加的两个信号接口进行管脚分配,将以下两条语句添加到testled.ucf中即可:NET "uart_rx" LOC = N17;NET "uart_tx" LOC = N18; 最后重新编译整个ISE工程并生成.bit下载文件。接下来要看软件的了,打开SDK并定位Workspace到本实例工程的

- Nexys3学习手记3:硬件外设走马观花(02-11)

- Nexys3学习手记5:流水灯在线运行(02-11)

- Nexys3学习手记7:MicroBlaze小试牛刀(02-11)

- Nexys3学习手记6:ClockingWizard探秘(02-11)

- Nexys3学习手记2:建立自己的开发环境(02-11)

- 基于CC1010的智能小球测风系统设计(06-28)