Xilinx可编程逻辑器件设计与开发(基础篇)连载48:Spartan

12.2.7 PicoBlaze 指令存储器配置方式

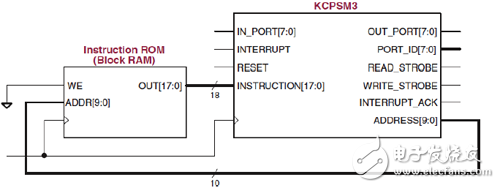

PicoBlaze微控制器实际上包含两个部分,分别是内核KCPSM3 和指令存储器ROM。为了确保在程序运行期间不会有写入操作,BRAM 的WE 端接地,如图12-18 所示。当然,除了这种方式,还会有多种其他方式,下面将一一介绍。

图12-18 PicoBlaze 微控制器存储器的标准配置1K&TImes;18

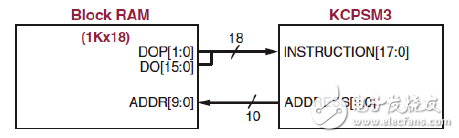

应用程序被编译后并被综合作为FPGA 实现的一部分,与FPGA 的配置文件.bit 一起存储,在FPGA 的配置过程中,应用程序被自动装入BRAM,如图12-19 所示。

图12-19 1K&TImes;18

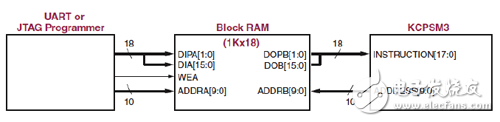

应用程序被编译后,可以不用再次与FPGA 一起综合,BRAM 数据即可通过JTAG 或者UART 被写入,如图12-20 所示。

图12-20 1K&TImes;18(具有UART 或JTAG 编程)

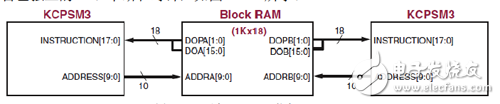

两个PicoBlaze 共享同一个BRAM,尽管他们执行相同的代码,但是每个微控制器都是单独执行,有自已独立的IO、中断和时钟,如图12-21 所示。

图12-21 两个PicoBlaze 共享1K&TImes;18

将一个BRAM 分成两块,供两个PicoBlaze 使用。注意地址位ADDRESS[9]的接法。配置方式如图12-22 所示。

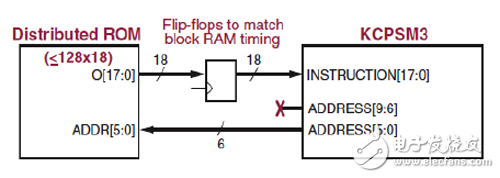

用分布式RAM 实现PicoBlaze 的指令存储器,比较适合于指令比较少的应用,因为分布式RAM 会消耗LUT 资源,如果RAM 容量太大,会影响逻辑的实现。配置方式如图12-23 所示。

图12-23 用分布式RAM

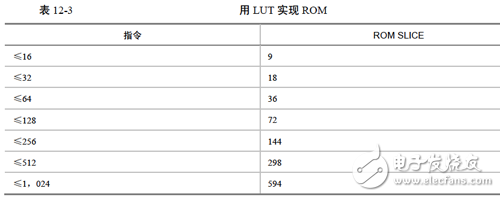

表12-3 为实现不同深度ROM 时SLICE 的消耗情况。

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)