摩尔定律:我这一辈子,见证了电子产业的崛起

国际电子设备大会上,摩尔对于此处修正过后的定律做出了解释,其切入点就是解答集成芯片上的元件是如何实现翻倍这一存在于人们心中的疑惑。摩尔指出有三个因素导致了这一趋势:不断缩小的元件体积,不断增长的芯片面积以及「工程智慧」,也就是说工程师们可以减少集成芯片上晶体管之间无用的空间。

摩尔认为之所以摩尔定律能够不断被实践所证明,有一半要归功于前两种要素,其他则全是「工程智慧」的功劳。但是摩尔表示一旦英特尔公司所生产的 CCD 内存投入市场之后,工程智慧可能就不再那么需要了。在 CCD 内存中,所有的元件排列的非常紧密,它们之中将不再会存在被浪费的空间。因此摩尔再次预测随着晶体管越来越小,集成芯片越来越大,集成芯片上的元件数量翻倍增长所用的时间将会越来越少。在 1965 年时他曾预测这个数量会每两年增长一倍,现在他将这个速度修正到了每年增长一倍。

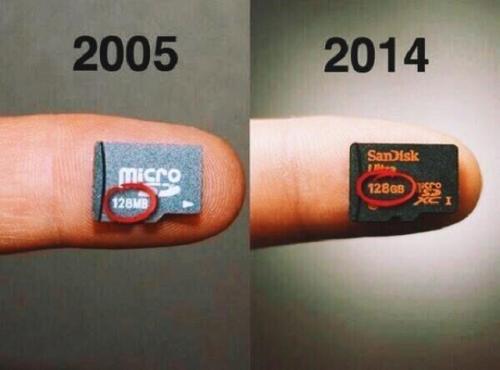

不过具有讽刺意味的是,由于 CCD 内存被证明很容易出错,所以英特尔公司根本就没有发行该产品。但是摩尔的预测却在逻辑芯片、微处理器的发展中得到了证实,从上世纪七十年代初期开始,这些芯片就已经按照了每两年所包含元件翻一番的速度在发展。而包含了大规模相同晶体管的内存芯片其发展速度就更快了,已经达到了每隔十八个月其包含元件就翻一番的速度,达到这一增长速度大部分要归于其设计工艺更为简单。

在影响摩尔定律实现的三个要素中,有一个要素是需要特殊对待的,那就是缩小晶体管的尺寸。至少在可见的一段时间范围内,缩小晶体管的尺寸是必须为之的,在这个问题上不存在权衡问题。根据 IBM 工程师 Robert Dennard 提出的缩放比例定律(译者注:缩放比例定律,随着芯片上晶体管数量的增加,功率密度必须保持不变),新一代的晶体管总是在不断进步。尺寸缩减的晶体管不仅仅是的集成电路可以包含更多的元件,同时也让晶体管本身工作的更快、耗能更少。

晶体管的尺寸问题直接影响到了摩尔定律是否能持续发挥作用,在不断发展的过程中,针对晶体管产生了截然不同的处理方法。在被我们成为摩尔定律 1.0 的早期阶段中,集成芯片的性能想要有所提升,通常需要依靠「扩容」——也就是在芯片上添加更多的电子元件。起初,想要实现这一目标看上去比较简单,只要将包含了电子元件的各类应用程序进行可靠且廉价的打包起来就行。但是这种做法的结果是使得集成芯片变得越来越大,也越来越复杂。在上世纪 70 年代初期,为了解决这一问题,微处理器诞生了。

不过在过去的几十年中,半导体行业的长足进步主要是由摩尔定律 2.0 推动的。这个阶段被人们称作「缩减」,也就是说在集成芯片上所包含的晶体管数量不变的情况下,缩小晶体管的尺寸并且降低其制作成本。

虽然摩尔定律 1.0 时代与 2.0 时代在时间上有所重合,但是在半导体产业的发展过程中可以看出「缩减」相比「扩容」是逐渐占据了主导地位。在上世纪 80 年代到 90 年代初期,半导体技术就发展到了一个关键「节点」上,我们将这一发展时期称为「RAM 时代」,在 1989 年出现了 4M DRAM,而到了 1992 年 16-MB DRAM 也出现了。每一次进化都意味着集成芯片的工作能力变得更强大,因为在不增加成本的情况下单个芯片中所能包含的晶体管变得越来越多。

在上世纪 90 年代初期,我们开始更多地依靠「缩减」来革新晶体管。选择这条发展道路是很自然而然的,因为大多数的芯片不再需要尽可能多地包含晶体管。集成电路在此时已经开始被大规模地运用于汽车、电子设备甚至是玩具之中,正因为如此,为了提高集成电路的性能并且降低制作成本,如何减小晶体管的尺寸已经成为了关键问题。

最终,即使技术允许,微处理器的体积也不再像之前一样不断扩大。虽然现在的制造技术已经能够实现在逻辑芯片上安放 100 亿个晶体管,但是在实践之中很少有集成芯片会达到这一数值。这在很大程度上来说,是因为集成芯片的设计已经跟不上了。

摩尔定律 1.0 至今仍然运用在图形处理器、现场可编程器件以及针对少数超级计算机的微处理器中,但是除此之外,摩尔定律 2.0 已经占据了统治地位。不过时至今日,这个定律继续在发生变化。

改变正在发生

这种改变其实已经开始了,因为晶体管小型化所带来的好处正逐步减少。这个趋势出现在 2000 年左右,在那时一种令人并不愉快的现实逐步显现出来。在当时,晶体管的尺寸已经开始缩小到 100 纳米以下,根据 Dennard 此前提出的缩放比例定律,缩减法则已经达到了极限。晶体管的体积变得

- 非一般的晶体管(10-12)

- 后摩尔定律时代,SoC设计者应关注的新方向(08-23)

- 后摩尔定律时代:终于跨越鸿沟?(06-27)

- 从Multicore到Many-Core:体系结构和经验(10-19)

- 7nm处理器是极限么?(09-21)

- 一文读懂SIP与SOC封装技术(09-29)