后摩尔定律时代:终于跨越鸿沟?

在20nm制程前期,是否有听过"摩尔定律终将失效"、"传统2D缩放在先进制程是行不通的"这些论述?但在实际中,又看到了什么呢?事实与这些预测大相径庭。

摩尔定律并未失效。可能无法像以前那样自动跳到下一世代制程,不过可以看到有很多公司在进行20 nm及以下的设计开发。遵循2D 电晶体缩放是一种保守的方法。对于那些有意义的设计类型,只要技术上和经济上可行,公司都会继续沿用。

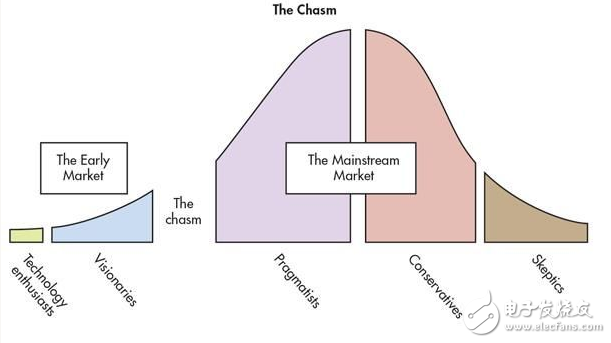

3D-IC已在特殊应用中取得了初步成功,但随后就深陷Geoffrey A. Moore在Inside the Tornado中描述的技术采用生命周期的"鸿沟"。

对3D-IC的共识是其进入了摩尔技术采用生命周期的鸿沟。

Samsung、Hynix和Micron创建了混合存储器立方联盟,其主要目的是建立并启用混合存储器立方。立方是一个创新的DRAM存储器架构,将高速逻辑制程技术与一叠矽通孔(TSV)粘合存储器芯片结合。

许多公司正在进行基于矽的CMOS图像感测器的开发,其将可用于大量潜在应用中,包括指纹图案成像、生物传感,以及电子快门控制。通过光子和电子的密集集成,在单一芯片上微型化复杂光子功能,从而使光子器件在大型写入领域具有纳米级精度,实现真正的大规模光子积体电路。

可以从这些早期市场应用中得出一些有趣的结论。围绕3D-IC的最初炒作是其提供了一种方法,通过将电晶体封装得更紧密并在相邻芯片上进行精细逻辑分区,进而继续开发新的缩放途径。即使在今天,早期市场应用也还未实现这一方法。这些2.5/3D-IC应用使用粗略设计分区,并通过更紧密的电晶体封装获得速度之外的其他优势。3D-IC为这些早期应用带来了实际价值,但并未如大家预测的那样解决摩尔定律的缩放问题。

是什么因素导致3D-IC至今无法跨越鸿沟或脱离幻灭低谷期?看来原因主要有几点:开始用力太猛;过于干扰目前的方法;缺少吸引力和客户口碑,以及成本。在技术采用生命周期中,早期采用者(如技术爱好者和有远见者)力争成为首个采用新技术之人,并将其作为一种手段,以此挣脱传统方法,进而创造引人注目的竞争力/业务差距。

相反,在主流市场上,实用主义者出于自身考虑,对新技术并不着迷。他们更喜欢对自己的制程、流程和设计方法进行改进。他们希望看到同行企业令人信服的成功案例以及市场领先供应商提供的解决方案,他们想要一个保守中具有商业意义的解决方案。

TSMC基于矽仲介层的2.5D-IC CoWoS参考流程以及GlobalFoundries的同类产品和领先的外包装配和测试(OSAT)厂是很有趣的初步尝试,可以创建主流市场更能接受的解决方案。早期使用者采用这些基于矽仲介层的高级封装在市场上已取得了一些成绩。但据目前所知,受限于仲介层的成本,无法对其进行广泛部署。这个成本问题可以简单归结为仲介层成为必须使用传统晶圆光刻工艺制造的另一个芯片。

低成本的解决方案可能改变游戏规则,而且有人可能会采用业界领先公司提供的扇出晶圆级封装(FOWLP)。据伯恩斯坦研究公司透露,TSMC有望将集成扇出(InFO)技术应用到批量生产中,是TSMC的FOWLP变型。

伯恩斯坦的Mark Li讲述了这种新封装方法的一些优势:InFO删去了封装中的基底,因此手机SoC的厚度从1 mm降到0.8 mm或更低。根据Li的说法,缩短逻辑芯片和印刷电路板之间的距离,可以加快散热、获得较高的最大容许功耗,也可能提供20%的性能(即使有功率损耗)。

据伯恩斯坦预测,如果这项技术取得市场上的成功,可能会成为使3D-IC跨越鸿沟进入主流市场的重大事件。引进这一技术,通过业界领先公司引人注目的成功案例和市场领先供应商的整套解决方案可打消典型"实用主义者"的所有顾虑。混用隐喻(或模式,因情况而异)来说,如果3D-IC最终进入光明复甦期并冲击主流市场,2016年应是奋进的一年。 (本文由Mentor Graphics公司Calibre物理验证产品市场行销总监Michael White提供,记者吴冠仪整理)

- 封测领域风云再起 巨头布建3D IC封测产能(06-30)

- 通过应用案例告诉你:赛灵思如何做到领先一代(02-12)

- 赛灵思专家:薄化制程良率升级,2.5D硅中介层晶圆成本下降(03-11)

- UltraScale可编程架构如何解决互连问题?(06-09)

- 如何打破3DIC设计与电源完整性之间的僵局(08-22)

- 赛灵思ASIC级UltraScale架构要素及相关说明(06-09)