FPGA+DSP架构的视频处理系统设计详解

本系统采用基于FPGA与DSP协同工作进行视频处理的方案,实现视频采集、处理到传输的整个过程。

实时视频图像处理中,低层的预处理算法处理的数据量大,对处理速度要求高,但算法相对比较简单,适合于用FPGA进行硬件实现,这样能兼顾速度及灵活性。高层的处理算法结构复杂,适用于运算速度高、寻址方式灵活、通信机制强的DSP芯片宋实现。

DSP+FPGA架构的最大特点是结构灵活、有较强的通用性、适合于模块化设计,从而能够提高算法效率,同时其开发周期短、系统易于维护和升级,适合于实时视频图像处理。

系统采用模块化的设计方法,将整个系统划分为三部分:视频采集单元、视频处理单元和视频传输单元。

整个系统以FPGA作为核心控制单元并完成视频信号的中值滤波工作;以DSP作为整个系统的核心处理单元对采集的视频图像信息进行JPEG压缩;在视频传输单元设计了以PDIUSBD12芯片为基础的USB总线,负责视频信号的传输。

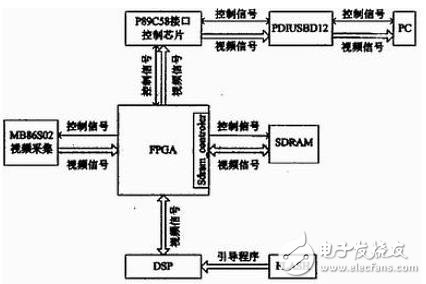

1系统硬件总体架构

一个完整的视频处理系统,主要由视频采集单元、视频处理单元及视频传输单元三部分组成。在进行系统设计时须确保各部分的无缝衔接。

图像采集单元由FPGA和MB86S02视频采集芯片组成,包括视频信号的采集和预处理,把输入的视频信号转换成系统能够处理的数字图像数据,并按照一定的格式存储在确定的存储区域。

图像处理单元是本系统的核心,对图像数据进行压缩处理,实现系统要达到的功能。

图像传输单元采用FPGA+USB的方式实现视频数据的传输,通过基于PDIUSBD12芯片的USB总线,将压缩后的视频图像信息发送到接收端,在接收端使用在PC上编写的应用程序将图像解压缩并显示出来。

整个硬件系统由FPGA和DSP两个分系统组成,FPGA作为视频采集单元,将采集到的视频信号预处理后传给DSP,DSP作为图像处理单元是本系统的核心,对FPGA预处理后的视频图像信息进行JPEG压缩处理,DSP单元的性能决定着整个系统的性能,DSP完成图像处理任务后,将把结果返回给 FPGA,FPGA将经过压缩处理后的图像信息写入接口控制芯片的数据缓冲区,由接口控制芯片负责信息的传输,系统总体框图如图1所示。

图1系统总体结构图

如图1所示,MB86S02视频图像传感器在FPGA的控制下进行视频图像信息的采集,在收到PC机的采集命令后MB86S02开始视频信号的采集 FPGA作为系统的核心控制单元不仅负责视频图像的采集,而且负责视频图像信息的预处理和系统各单元模块之间的数据交互。针对视频图像数据量大的特点,为了保证系统的实时性要求,系统采用大容量的片外SDRAMR对采集到的视频图像信息进行缓存,SDRAM控制器由FPGA实现,视频图像信息经过 SDRAM缓存后首先要由FPGA对其进行滤波处理,以消除图像信息中的噪声干扰,本系统中采用中值滤波的方式对采集到的视频信息进行处理,滤波后的数据通过FPGA内部FIFO进入DSP进行下一步的压缩处理。DSP上电后首先进行引导程序的自加载,等待FPGA发送请求,在收到FPGA的请求后,DSP建立EDMA通道从FPGA获取视频数据,存满一帧后,开始对视频图像进行JPEG压缩处理,压缩处理后的视频图像信息经过FIFO缓存后,在 FPGA的控制下写入USB接口控制器的数据缓存区,等待PC机的读数请求,USB接口控制器在收到PC机的读数请求后将数据写入PDIUSBD12的端口1,以便PC机下一步读取数据。

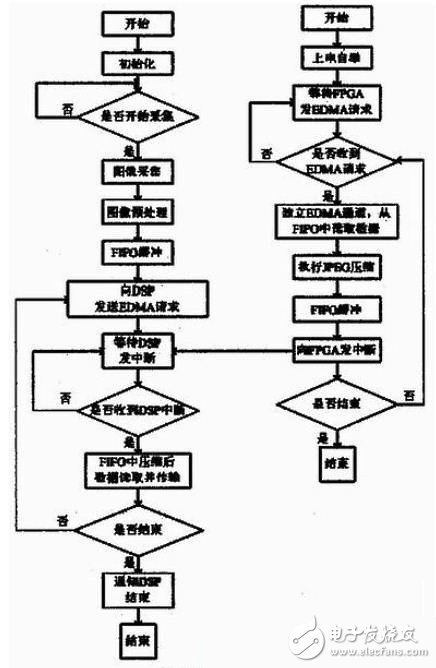

2系统软件总体设计

系统的软件设计根据硬件结构的总体划分,也可以分为两大部分来描述。整个系统的运行如图2所示,FPGA和DSP各自的程序独立运行,通过中断信号完成数据的实时交互。FPGA向DSP方向的指令是通过FPGA发送一个EDMA请求,DSP通过响应EDMA请求,建立EDMA通道,开始从FIFO中进行预处理后数据的读取,DSP向FPGA传输数据时,通过向FPGA发送一个中断信号,让其从FIFO中把压缩后的图像数据读出来。

图2系统软件软件流程图

如图2所示,整个系统工作流程可以简单描述如下:系统上电后,首先DSP由flash实现自举,并运行引导程序,之后转入EDMA等待状态,FPGA初始化后等待外部图像采集命令,收到图像采集命令后开始进行图像采集,并对采集到的图像进行预处理,预处理后的图像经过FIFO缓冲,在存储一定量的数据之后,FPGA通过半满信号向DSP发送EDMA请求,等待DSP响应,DSP一旦收到来自FPGA的EDMA请求,立即建立EDMA通道,从FIFO中读取数据到L2存储器,存满一帧图像后DSP开始图像压缩,等待一幅图像压缩完成之后,DSP会向FPGA发送中断信号,FPGA在收到中断信号后开始从 FIFO中读取压缩后的图像数据。一帧数据读完后,判断编

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)