DSP in FPGA:FIR滤波器(二)

,可以发现预加器配对数据中有一个数据始终是x(n-12),但是每一个配对数据的相对延时与常规情况下相同:10、8、6、4和2。

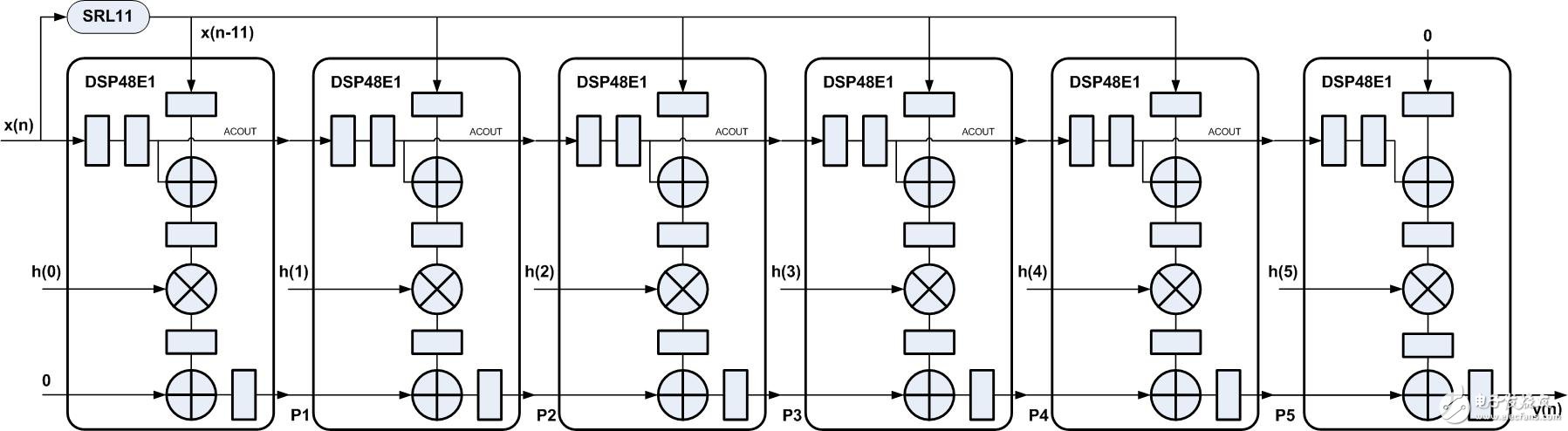

图3

而各节点P1、P2、P3、P4、P5和y(n)的表达式如下

P1=x(n-5)h(0) + x(n-15)h(0)

P2=( P1 + (x(n-6)h(1) + x(n-14)h(1)) )Z-1=x(n-6)h(0) + x(n-16)h(0) + x(n-7)h(1) + x(n-15)h(1)

P3=( P2 + (x(n-8)h(2) + x(n-14)h(2)) )Z-1=x(n-7)h(0) + x(n-17)h(0) + x(n-8)h(1) + x(n-16)h(1) + x(n-9)h(2) + x(n-15)h(2)

P4=( P3 + (x(n-10)h(3) + x(n-14)h(3)) )Z-1=x(n-8)h(0) + x(n-18)h(0) + x(n-9)h(1) + x(n-17)h(1) + x(n-10)h(2) + x(n-16)h(2) + x(n-11)h(3) + x(n-15)h(3)

P5=( P4 + (x(n-12)h(4) + x(n-14)h(4)) )Z-1=x(n-9)h(0) + x(n-19)h(0) + x(n-10)h(1) + x(n-18)h(1) + x(n-11)h(2) + x(n-17)h(2) + x(n-12)h(3) + x(n-16)h(3) + x(n-13)h(4) + x(n-15)h(4)

y(n)=(P5 + x(n-14)h(5))Z-1= x(n-10)h(0) + x(n-20)h(0) + x(n-11)h(1) + x(n-19)h(1) + x(n-12)h(2) + x(n-18)h(2) + x(n-13)h(3) + x(n-17)h(3) + x(n-14)h(4) + x(n-16)h(4) + x(n-15)h(5)

因抽头系数对称,由h(0)=h(10),h(1)=h(9),h(2)=h(8),h(3)=h(7),h(4)=h(6)可得

y(n)= x(n-10)h(0) + x(n-11)h(1) + x(n-12)h(2) + x(n-13)h(3) + x(n-14)h(4) + x(n-15)h(5) + x(n-16)h(6) + x(n-17)h(7) + x(n-18)h(8) + x(n-19)h(9) + x(n-20)h(10)

验证得到y(n)=yt(n-10),比普通脉动结构延时小,但是相比于其他结构的FIR滤波器延时还是较大的。

编写了相关代码,综合结果如下:

Number of Slice Registers: 84

Number of Slice LUTs: 99

Number of DSP48E1s: 6

Minimum period: 3.256ns{1} (Maximum frequency: 307.125MHz)

在DSP in FPGA: FIR滤波器设计(一)、(二)中分别讲解了直接型、转置型和脉动型结构FIR滤波器的实现方法,这三种结构是FPGA实现中比较常用的方法,以下对这三种结构做一个比较:

(1) 直接型:方法简单易实现,但是使用加法树优化后增加了功耗

(2) 转置型:关键路径延时较小,时序易满足,但是输入数据扇出较大,不适用于阶数较高的滤波器实现

(3) 脉动型:适用于高速数据处理,但是延时相比于其它结构较大

- 详解FIR滤波器和IIR滤波器区别(04-04)

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)