如何调试数字硬件设计?

件底层模块是否适合做进一步的测试。相关检查包括模块的初步通电测试,这是个紧张的过程。刚拿到模块,您希望确保其准确投产,能够成功实现首次通电启动。第一步就是确保所有的组件都各就其位,引脚"1"正确定位,而且任何带极性的组件都准确放置。设计中通常可能包含众多无需检查定位的组件,例如那些适合不同版本或不同构建选项的组件。

如果您确定所有电源轨都没有短路,那么下一步就该加电了。初次加电时,我倾向于采用分两个阶段进行的方案。第一个阶段是采用低电压(0.5V)和低电流,以确保不错过信号层或电压轨之间的任何短路情况;第二个阶段是用正确的工作电压在设定的电流限值内加电,看看是否获得预期电流(不要忘了突入电流问题)。

成功给设计方案加电后,下一步就是确定电源上电的排序、复位以及时钟是否能按设想的工作。切记,要确保复位时长超过所有时钟,并在释放之前处于稳定状态。

明确硬件特性的下一步就是确保能通过JTAG链看到硬件,这使我们不仅能对FPGA编程,而且还能执行边界扫描测试。边界扫描测试能帮助我们快速测试器件之间的互连,通过测试存储器可确保其正常工作,如开发回环接插件也可回转输入输出。JTAG和边界扫描测试可在进一步详细的测试之前消除设计风险。

致力于简化RTL

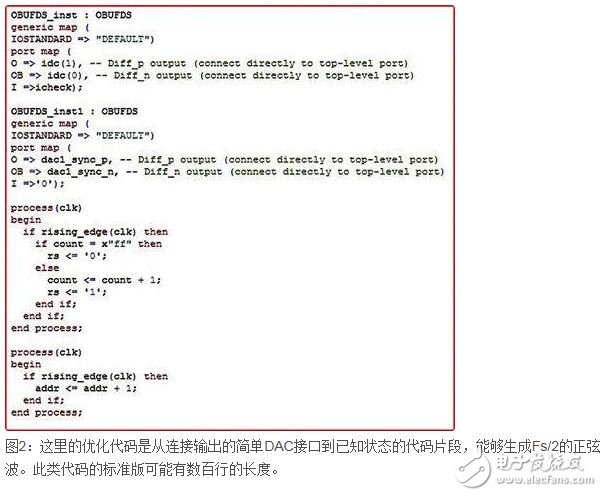

如果您的设计在硬件和FPGA层面上都很复杂,那么简化版的RTL将有助于测试开发板以及FPGA和外设(图2)之间的接口。对高速接口设计而言,更是如此。我们可结合采用优化的RTL和赛灵思 ChipScope工具来捕获数据,以及预载了数据模式的Block BRAM来发挥激励作用。这种方法对采用ADC和DAC连接FPGA的情况尤其有用。在此情况下,您应发挥FPGA的可再编程特性来最大限度地进行设计开发,实现ADC和DAC的参数测试,比如噪声/功率比、无杂散动态范围和有效比特位数(effective-number-of-bit)计算等。

此外,您还应该充分利用FPGA提供的资源,尤其是赛灵思System Monitor和XADC,非常有利于监控芯片上的电压轨,进而还能有助于验证在设计阶段所执行的电源完整性分析。此外,上述技术还能方便地报告芯片温度,这对环境测试以及芯片温度的功耗关联等都有帮助。

多数情况下,简化RTL设计并采用FPGA提供的资源对精确定位未按预期工作的区域都有极大的帮助。

遇到问题怎么办?

在一步步推进测试计划的过程中,您可能会遇到一两个问题,如未能实现预期的功能,或在功能方面无法满足所需的性能水平。不要担心,我们能通过许多调查方法来确定问题根源和所需的纠正措施。

在上述情况下,不要急于马上做出修改。首先,要重新检查设计方案,特别是原理图和数据手册等设计信息。如果问题与FPGA有关,则应检查引脚约束文件是否适合设计需要,因为有可能文件与设计不同步。

如果一时找不出什么明显错误,则不妨发挥一下互联网的优势,去网上看看其他工程师是否也遇到过跟您同样的问题。网上有很多论坛,您可在那里向其他设计人员提问。Programmable Planet和赛灵思论坛都可为基于FPGA的设计提供广泛的支持。

说到底,硬件调试是工程设计中极富挑战,但又极具收获的组成部分。若在设计早期阶段即考虑到测试问题,并在设计中包含测试所需的各元素,就能显著简化调试工作。采用ChipScope、System Monitor和XADC等所有可用的资源来调试系统,外加合理利用传统测试设备,我们就能成功完成开发工作。

- 单片机开发过程中硬件调试技巧(05-02)

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)