基于FPGA的多路光栅信号采集方案

0 引言

光栅传感器作为精密机械量测量的有效工具在线位移、角位移、速度、加速度等工程的测量上得到了广泛应用。在长度测量中,光栅微位移传感器可以达到μm级的测量精度,同时可以动态采集长度的变化,从而可以精确地算出运动速度甚至加速度。在曲面测量中,相比于传统的三坐标机、轮廓仪,光栅传感器也具有可以动态检测面形变化,精度高,可以实时输出面形数据等优势。

多路选择技术的数据采集中得到了广泛应用,在一些分布式系统当中,使用多路选择技术可以减少I/O 口使用数量,提高系统集成度。具体来说,使用多路选择开关对多路信号进行选通处理,将多路选择开关的输出端连接采集芯片的I/O口,使采集芯片对各路信号进行轮番采样,但轮番采样使得原始波形的采集离散化,即在芯片对采得的离散信号进行处理前,需要对采得的波形进行处理。

1 系统整体方案

系统选用了60 支高精度光栅传感器(精度为0.5 μm),按环带状排布,以测量圆状动态面形变化。

实际测量时,60个光栅微位移传感器安放在测量台上,待测面形与各传感器接触,待测面形变化时,各路光栅传感器会产生相应的位移,将面形各采集点处的数据变化采集起来,通过一定的插值算法还原面形的动态变化。

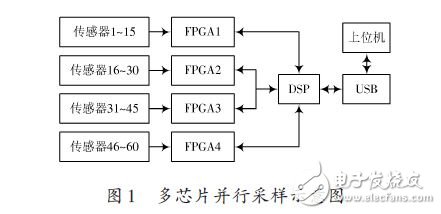

通常情况下,采集系统选用FPGA作为光栅信号的采集芯片。因系统涉及的信号路数较多,单片低端FPGA 很难满足信号采集的要求,故需要多片FPGA 并行工作,最后用一片DSP芯片或单片机对多片FPGA进行轮番寻址取值,再将各传感器的数据传送给上位机,如图1所示。系统结构设计较为复杂,成本也较高。

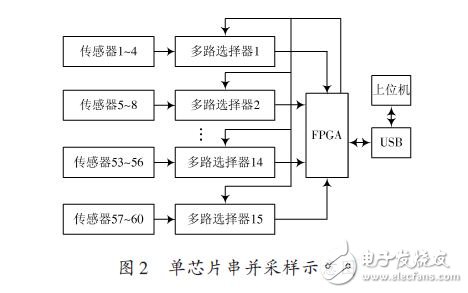

本文提出了一种基于多路选择技术的多路信号采集方案,针对多路信号无法同时被单芯片采集的问题,采用串、并结合采样的方法,可以在满足采样精度要求的情况下,实现单FPGA上的多路信号采集,如图2所示。

每个传感器输出信号中,表示传感器移动距离的信号有两路(A、B)。4 个传感器分为一组,共有8 路信号(1A、…、4A,1B、…、4B)。将1A~4A 接双4 位多路选择开关(如74HC4052)的1Y0~1Y3,1B~4B 接多路选择开关的2Y0~2Y3.FPGA发出2位控制信号同时控制该多选芯片MUX1.即FPGA控制信号为00时,MUX1的1Z输出为1A,2Z输出为1B,此时FPGA接收到的信号为传感器1 的信号。FPGA 的控制信号进入下一个状态01时,MUX1的1Z 输出为2A,2Z 输出为2B,此时传感器2的信号被采集。依次类推,传感器4的信号之后重新返回到传感器1上。这样就形成一个循环采样的过程。

在对采样频率要求不高时,多路并行采样可以节省很多IO资源,同时精度也可以得到保证。FPGA内部用状态机可以完成多路选择的控制,如图3所示。

2 光栅信号预处理

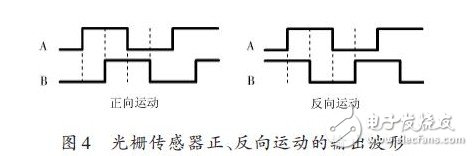

光栅位移传感器输出为两路相位相差90°的方波信号,如图4所示,正常情况下可以通过两路波形的上升、下降沿的个数来计量位移的实际变化;并由两路信号的瞬时相位变化得出位移的移动方向。但由于本方案使用循环采样的方法,使得某路光栅信号只有14 被采集到,故需通过相关方法还原原始信号。

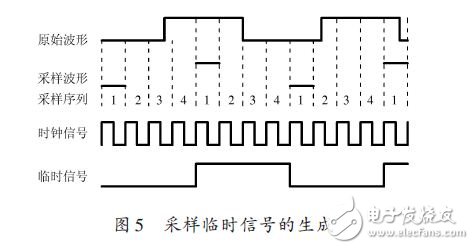

这里采用通过滤波引入临时信号的方法,将采集信号通过时钟延时将采样波形保持为采样值四个时钟周期,生成类似于原始信号的临时信号,如图5所示。

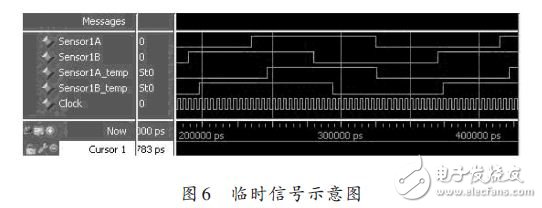

滤波的作用是消除毛刺等噪声对采样信号产生的影响,常规的滤波方法为通过对若干个时钟周期内信号的判断来实现。当几个时钟周期内信号的值并未发生跳转时,认为信号值为真实值,可以作为进一步处理的临时信号,如图6所示。可以看出临时信号仅仅比原始波形信号滞后了若干时间(该滞后时间所对应的时钟周期数小于串行采样数,此处串行采样数为4),这样可以基本准确地还原原始的波形,细分辨向计数等操作基于该临时信号,当信号周期远大于时钟周期,即光栅信号变化缓慢时,对采样的精度基本没有影响。

3 多路光栅信号并行采集

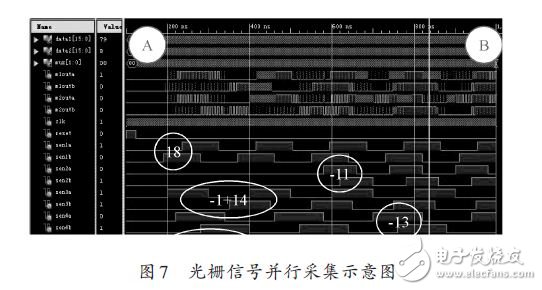

对8 路光栅信号按上述方法进行处理,如图7 所示。在图中所示范围内,传感器1~4产生以下信号:增加18、减少11、先减1再加14、减少13.

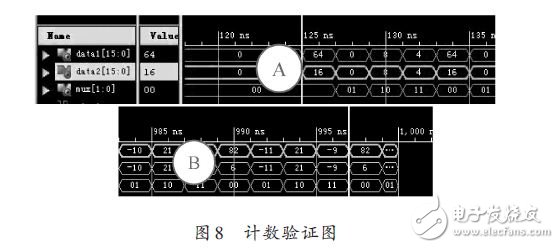

观察图中A、B两处的计数,如图8所示。A处传感器1~4的初始值为64,0,8,4,B处可见传感器1~4的计数值为82,-11,21,-9.与产生的脉冲信号完全符合,说明实现了正确的数据采集。

4 结论

本方案适用于低速且输入较多的数据采集装置,对于高速信号,信号周期与时钟周期相差倍数较小时,此法会造成有效信号的损失,并不适用。当信号周期远大于时钟周期时(Ts 》 20Tclk ),引入的临时信号仅仅比原始信号滞后几个

- 基于光栅传感器位移测量的方案设计(06-10)

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)