基于FPGA的数字核脉冲分析器硬件设计方案

3.4 电源电路

稳压电源通常有两类:线性稳压电源和开关稳压电源。开关电源的功率调整开关晶体管工作在开关状态,极易产生严重的开关干扰,若采用开关稳压电源,这些干扰将严重地影响数字多道分析器的正常工作,降低A/D转换精度。所以本文采用线性稳压电源为各功能模块供电。线性稳压电源的优点是输出电压比输入电压低,反应速度快,输出波纹较小,工作产生的噪声低。

本文设计的电源电路其输入电压为9~12 V,输出电压有5 V,3.3 V,2.5 V,1.8 V,1.2 V.线性稳压电路为单端转差分、ADC、FPGA、LVDS等各模块供电。

4 数字寻峰

NaI(Tl)探测器输出信号通过调理电路后进入高速ADC,ADC 进行连续高速的采样,然后由FPGA 完成数字核脉冲信号的积分、峰值检测、阈值判断等功能[8]。由于当核能谱达到峰值时,其一阶导数为0,据此可在连续的输入信号中找到各核脉冲的峰值,并 将该峰值对应道址的计数值加1,从而形成核能谱。为提高寻峰效率,寻峰之前需要对离散脉冲信号进行阈值判断,对幅值低于阈值下限的信号不进行寻峰处理,可 大大减少参与寻峰的离散核脉冲信号。

5 功能测试

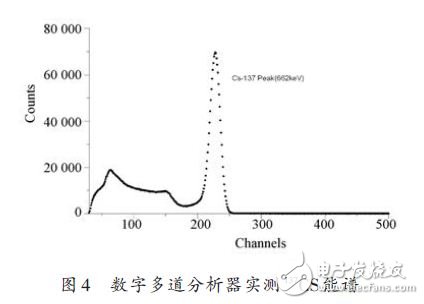

利用Borland C++集成开发环境开发了谱数据处理上位机软件,软件实现了能谱显示、能谱数据管理、系统参数设置、RS 485通信等功能。图4是本文设计的数字多道分析器分析137CS得到的1 024道能谱,其能量分辨率接近8%.

6 结语

本文提出了一种基于FPGA的数字核脉冲分析器硬件设计方案。该方案在单片FPGA中实现了多道脉 冲幅度的数字分析功能,通过软件功能仿真和实际运行,说明了数字多道脉冲幅度分析器硬件设计的可行性,将FPGA 应用到数字能谱测量系统能充分发挥其并行处理优势,并能有效降低硬件电路设计的复杂度。(作者:崔辰元,曾卫华,陈宏,徐奥)

- 基于FPGA的数字核脉冲分析器硬件设计解析(05-09)

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)