赛灵思FPGA全局时钟网络结构详解

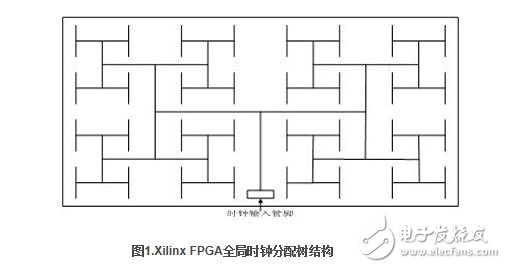

在 Xilinx 系列 FPGA 产品中,全局时钟网络是一种全局布线资源,它可以保证时钟信号到达各个目标逻辑单元的时延基本相同。其时钟分配树结构如图1所示。

针对不同类型的器件,Xilinx公司提供的全局时钟网络在数量、性能等方面略有区别,下面以Virtex-4系列芯片为例,简单介绍FPGA全局时钟网络结构。

Virtex- 4系列FPGA利用1.2V、90nm三栅极氧化层技术制造而成,与前一代器件相比,具备灵活的时钟解决方案,多达80个独立时钟与20个数字时钟管理器,差分全局时钟控制技术将歪斜与抖动降至最低。以全铜工艺实现的全局时钟网络,加上专用时钟缓冲与驱动结构,从而可使全局时钟到达芯片内部所有的逻辑可配置单元,且I/O单元以及块RAM的时延和抖动最小,可满足高速同步电路对时钟触发沿的苛刻需求。

在FPGA设计中,FPGA全局时钟路径需要专用的时钟缓冲和驱动,具有最小偏移和最大扇出能力,因此最好的时钟方案是由专用的全局时钟输入引脚驱动的单个主时钟,去钟控设计项目中的每一个触发器。只要可能就应尽量在设计项目中采用全局时钟,因为对于一个设计项目来说,全局时钟是最简单和最可预测的时钟。

在软件代码中,可通过调用原语IBUFGP来使用全局时钟。IBUFGP的基本用法是:

IBUFGP U1(.I(clk_in), .O(clk_out));

全局时钟网络对FPGA设计性能的影响很大,所以本书在第11章还会更深入、更全面地介绍全局时钟网络以及相关使用方法。

DCM模块的使用

1.DCM模块的组成和功能介绍

数字时钟管理模块(Digital Clock Manager,DCM)是基于Xilinx的其他系列器件所采用的数字延迟锁相环(DLL,Delay Locked Loop)模块。在时钟的管理与控制方面,DCM与DLL相比,功能更强大,使用更灵活。DCM的功能包括消除时钟的延时、频率的合成、时钟相位的调整等系统方面的需求。DCM的主要优点在于:

(1)实现零时钟偏移(Skew),消除时钟分配延迟,并实现时钟闭环控制;

(2)时钟可以映射到PCB上用于同步外部芯片,这样就减少了对外部芯片的要求,将芯片内外的时钟控制一体化,以利于系统设计。对于DCM模块来说,其关键参数为输入时钟频率范围、输出时钟频率范围、输入/输出时钟允许抖动范围等。

DCM 共由四部分组成,如图2所示。其中最底层仍采用成熟的DLL模块;其次分别为数字频率合成器(DFS,Digital Frequency Synthesizer)、数字移相器(DPS,Digital Phase Shifter)和数字频谱扩展器(DSS,Digital Spread Spectrum)。不同的芯片模块的DCM输入频率范围是不同的,例如:

1)DLL模块

DLL 主要由一个延时线和控制逻辑组成。延时线对时钟输入端CLKIN产生一个延时,时钟分布网线将该时钟分配到器件内的各个寄存器和时钟反馈端CLKFB;控制逻辑在反馈时钟到达时采样输入时钟以调整二者之间的偏差,实现输入和输出的零延时,如图3所示。具体工作原理是:控制逻辑在比较输入时钟和反馈时钟的偏差后,调整延时线参数,在输入时钟后不停地插入延时,直到输入时钟和反馈时钟的上升沿同步,锁定环路进入"锁定"状态,只要输入时钟不发生变化,输入时钟和反馈时钟就保持同步。DLL可以被用来实现一些电路以完善和简化系统级设计,如提供零传播延迟,低时钟相位差和高级时钟区域控制等。

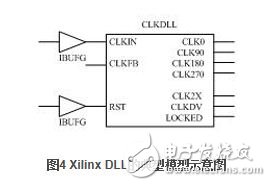

在Xilinx芯片中,典型的DLL标准原型如图4所示,其管脚分别说明如下:

CLKIN(源时钟输入):DLL输入时钟信号,通常来自IBUFG或BUFG。

CLKFB(反馈时钟输入):DLL时钟反馈信号,该反馈信号必须源自CLK0或CLK2X,并通过IBUFG或BUFG相连。

RST(复位):控制DLL的初始化,通常接地。

CLK0(同频信号输出):与CLKIN无相位偏移;CLK90与CLKIN 有90度相位偏移;CLK180与CLKIN 有180度相位偏移;CLK270与CL KIN有270度相位偏移。

CLKDV(分频输出):DLL输出时钟信号,是CLKIN的分频时钟信号。DLL支持的分频系数为1.5,2,2.5,3,4,5,8 和16。

CLK2X(两倍信号输出):CLKIN的2倍频时钟信号。

LOCKED(输出锁存):为了完成锁存,DLL可能要检测上千个时钟周期。当DLL完成锁存之后,LOCKED有效。

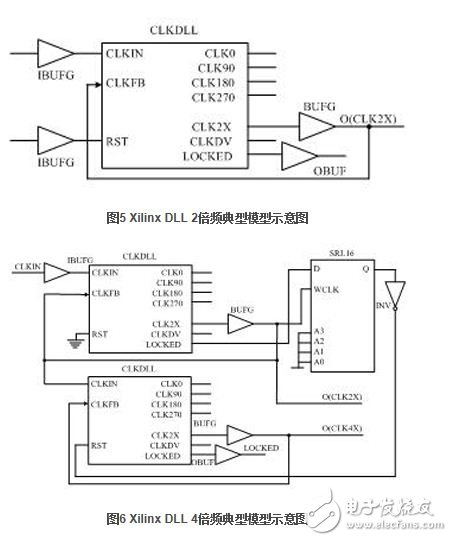

在FPGA 设计中,消除时钟的传输延迟,实现高扇出最简单的方法就是用DLL,把CLK0 与CLKFB相连即可。利用一个DLL可以实现2倍频输出,如图5所示。利用两个DLL 就可以实现4倍频输出,如图6所示。

2)数字频率合成器

DFS 可以为系统产生丰富的频率合成时钟信号,输出信号为CLKFB和CLKFX180,可提供输入时钟频率分数倍或整数倍的时

- 4G LTE技术很成功,对5G设计有何意义?(05-05)

- 物联网的承诺:下一个重大应用(02-16)

- Xilinx在2017嵌入式世界大会上展示响应最快且可重配置的视觉导向智能系统(02-17)

- 基于赛灵思FPGA的端到端广播平台解决方案的实现(10-27)

- 基于赛灵思(Xilinx) FPGA的DisplayPort设计与实现(10-23)

- 玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯(11-05)