赛灵思FPGA全局时钟网络结构详解

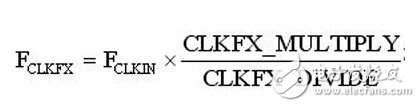

钟输出频率方案,输出频率范围为 1.5~320 MHz(不同芯片的输出频率范围是不同的)。这些频率基于用户自定义的两个整数比值,一个是乘因子(CLKFX_ MULTIPLY),另外一个是除因子(CLKFX_ divIDE),输入频率和输出频率之间的关系为:

比如取CLKFX_MULTIPLY = 3,CLKFX_divIDE = 1,PCB上源时钟为100 MHz,通过DCM 3倍频后,就能驱动时钟频率在300 MHz的FPGA,从而减少了板上的时钟路径,简化板子的设计,提供更好的信号完整性。

3) 数字移相器

DCM 具有移动时钟信号相位的能力,因此能够调整I/O信号的建立和保持时间,能支持对其输出时钟进行0度、90度、180度、270度的相移粗调和相移细调。其中,相移细调对相位的控制可以达到1%输入时钟周期的精度(或者50 ps),并且具有补偿电压和温度漂移的动态相位调节能力。对DCM输出时钟的相位调整需要通过属性控制PHASE_SHIFT来设置。PS设置范围为 -255到 255,比如输入时钟为200 MHz,需要将输出时钟调整 0.9 ns的话,PS =(0.9ns/ 5ns)?56 = 46。如果PHASE_ SHIFT值是一个负数,则表示时钟输出应该相对于CLKIN向后进行相位移动;如果PHASE_SHIFT是一个正值,则表示时钟输出应该相对于 CLKIN向前进行相位移动。

移相用法的原理图与倍频用法的原理图很类似,只用把CLK2X输出端的输出缓存移到CLK90、CLK180或者CLK270端即可。利用原时钟和移相时钟与计数器相配合也可以产生相应的倍频。

4) 数字频谱合成器

Xilinx 公司第一个提出利用创新的扩频时钟技术来减少电磁干扰(EMI)噪声辐射的可编程解决方案。最先在FPGA中实现电磁兼容的EMIControl技术,是利用数字扩频技术(DSS)通过扩展输出时钟频率的频谱来降低电磁干扰,减少用户在电磁屏蔽上的投资。数字扩频(DSS)技术通过展宽输出时钟的频谱,来减少EMI和达到FCC要求。这一特点使设计者可极大地降低系统成本,使电路板重新设计的可能性降到最小,并不再需要昂贵的屏蔽,从而缩短了设计周期。

2.DCM模块IP Core的使用

例:在ISE中调用DCM模块,完成50MHz时钟信号到75MHz时钟信号的转换。

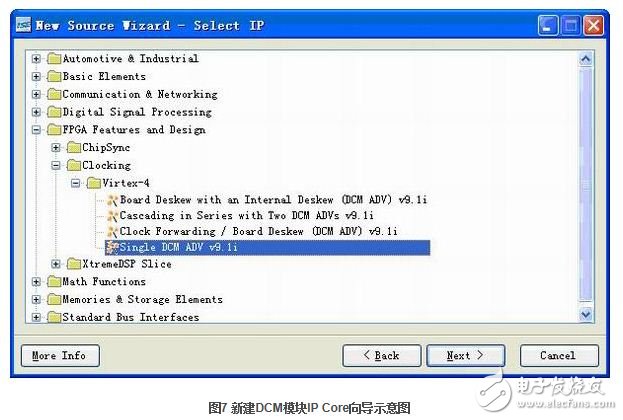

1)在源文件进程中,双击"Create New Source";然后在源文件窗口,选择"IP (CoreGen & Architecture Wizard)",输入文件名"my_dcm";再点击"Next",在选择类型窗口中,"FPGA Features and Design –

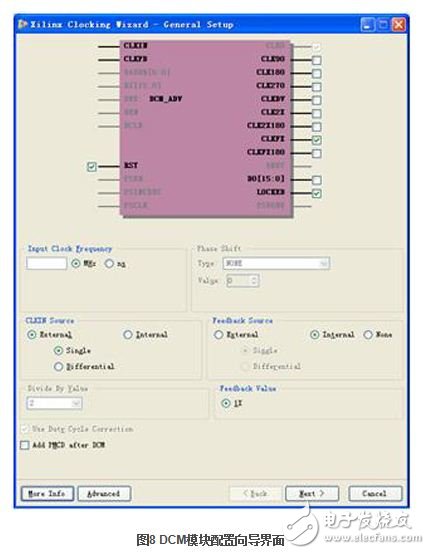

《2》 点击"Next","Finish"进入Xilinx 时钟向导的建立窗口,如图8所示。ISE默认选中CLK0和 LOCKED这两个信号,用户根据自己需求添加输出时钟。在"Input Clock Frequency"输入栏中敲入输入时钟的频率或周期,单位分别是MHz和ns,其余配置保留默认值。为了演示,这里添加了CLKFX 信号,并设定输入时钟为单端信号,频率为50MHz,其余选项保持默认值。

《3》 点击"Next",进入时钟缓存窗口,如图9所示。默认配置为DCM输出添加全局时钟缓存以保证良好的时钟特性。如果设计全局时钟资源,用户亦可选择"Customize buffers"自行编辑输出缓存。一般选择默认配置即可。

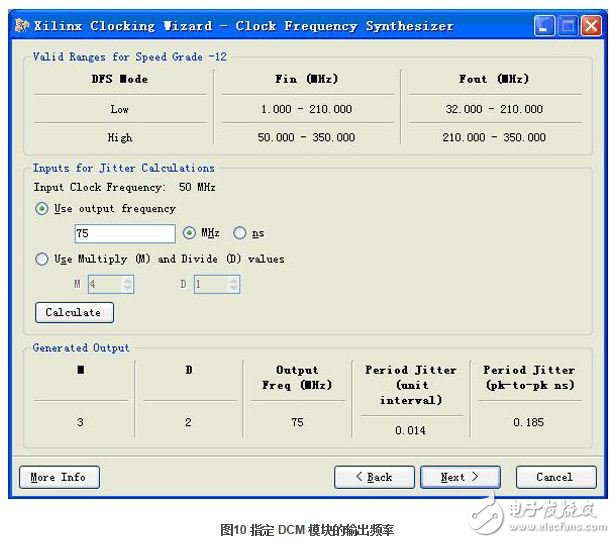

《4》 点击"Next",进入时钟频率配置窗口,如图10所示。键入输出频率的数值,或者将手动计算的分频比输入。最后点击 "Next","Finish"即可完成DCM模块IP Core的全部配置。本例直接键入输出频率为75MHz即可。

《5》 经过上述步骤,即可在源文件进程中看到"my_dcm.xaw"文件。剩余的工作就是在设计中调用该DCM IP Core,其例化代码如下:

module dcm_top(

CLKIN_IN,

RST_IN,

CLKFX_OUT,

CLKIN_IBUFG_OUT,

CLK0_OUT,

LOCKED_OUT);

input CLKIN_IN;

input RST_IN;

output CLKFX_OUT;

output CLKIN_IBUFG_OUT;

output CLK0_OUT;

output LOCKED_OUT;

mydcm dcm1(

.CLKIN_IN(CLKIN_IN),

.RST_IN(RST_IN),

.CLKFX_OUT(CLKFX_OUT),

.CLKIN_IBUFG_OUT(CLKIN_IBUFG_OUT),

.CLK0_OUT(CLK0_OUT),

.LOCKED_OUT(LOCKED_OUT)

);

endmodule

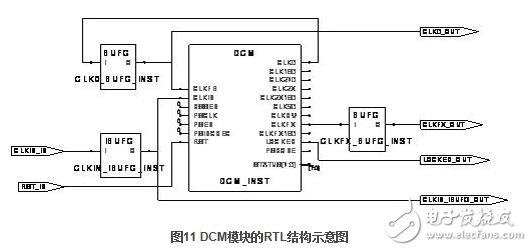

《6/》 上述代码经过综合Synplify Pro综合后,得到的RTL级结构图如图11所示。

上述代码经过ModelSim仿真后,其局部仿真结果如图12所示。从中可以看出,当LOCKED_OUT信号变高时,DCM模块稳定工作,输出时钟频率 CLKFX_OUT为输入时钟CLK_IN频率的1.5倍,完成了预定功能。需要注意的是,复位信号RST_IN是高有效。

在实际中,如果在一片FPGA内使用两个DCM,那么时钟从一个clk输入,再引到两个DCM的clk_in。这里,在DCM模块操作时,需要注意两点:首先,用Co

- 4G LTE技术很成功,对5G设计有何意义?(05-05)

- 物联网的承诺:下一个重大应用(02-16)

- Xilinx在2017嵌入式世界大会上展示响应最快且可重配置的视觉导向智能系统(02-17)

- 基于赛灵思FPGA的端到端广播平台解决方案的实现(10-27)

- 基于赛灵思(Xilinx) FPGA的DisplayPort设计与实现(10-23)

- 玩转赛灵思Zedboard开发板(3):基于Zynq PL的流水灯(11-05)