为空间飞行器量身打造:可自修复的空间电子系统设计

其中,姿态四元 数q=[q13 q4]T=[q1 q2 q3 q4],其 中q13 为矢量部分,q4 为标 量部分。u(t)为三个陀螺的测量输出值 ,ω(t)为沿三个陀螺输入轴的真实姿态角 速率,b(t)为三个 陀螺的常值漂移,d(t)为三个陀螺的相关漂移,n1 为三个陀螺 的测量白噪声,且n1 的三个分量服从N(0,σgi ),(i=x,y,z)。我 们将把此算法用HDL语言编制 成硬件并行 执行模块。当航 天器当前任 务阶段需要执 行此算法时,将其加载入部分重构模块。为此,我 们将在航天 器姿态确 定任务阶 段时,在其 中一个可 重配置区域 载入其算法硬件加速模块。其工作流程图如下:

图表 5 算法部分重配置工作流程图

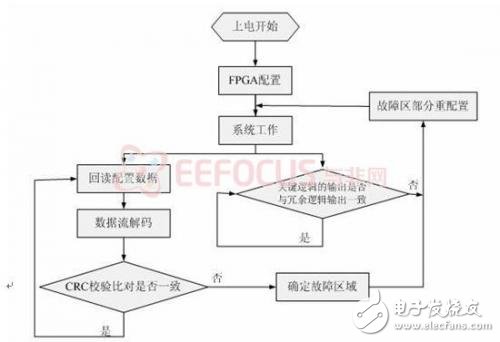

2.3 硬件故障检测与修复

在太空中 恶劣的环境 下,电子 系统在高 能带电粒子 的轰击下 很能会发生 状态翻转,导 致功能出错 ,甚至发 生致命的控 制错误。 为此,我们 设计模块 来回读 FPGA 中的配置数据 并进行 CRC 校验,发现数据错误后重新配置出错区域 ,及 时修复系统。

Virtex 系列 FPGA 系列包含了一个叫做回读的特性。它最 初是设计来方便芯 片生产时的测试。它提供了一种非侵入式的 读取 FPGA 中的每 个锁存器和配置 存储器状态的方法。要利用这个特性,需要在 设计中例化回读组件。这个功能实在后台运行的,不会影响 FPGA 的运行性能。FPGA 的设计可以 全速运行而同时运行回读功能。

在所有的读出的比特之上会产生一个 CRC 校验和,并把这个 校验和插入到回读序列流 的末尾。这 个校验和 通过和当前 配置下期 望的校验和 比对。如 果不匹配,一个 SEU 很可能就发生了。

我们将设计控制逻辑来运行和获取回读。 这个过程需要执行下面的步骤:

1,开始回读:把 RT 置高并保持住直 到回读结束。

2,从回读的开始到结束都不能打断 CLOCK。CLOCK 信号必须 在 1Mhz

和 2Mhz 之间。

3,把回读数据输入一个 6 位的解码器,以便 寻找数据头《111110》。

4,当字头被找到时,开始计数时钟周期,当达到前面表 格所示的计数值时,

接下来就是一个 0,接着就是 11bit 的 CRC。

5,把这个 CRC 与期望的 CRC 比对。

图表 6 故障检测与修复流程图

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)