分离栅极闪存循环擦写引起退化分量剖析

SuperFlash®技术基于分离栅极概念,广泛用于独立和嵌入式NOR闪存产品。与其他竞争解决方案相比,SuperFlash的主要优势包括:因采用较厚的隧道电介质层而具有卓越的可靠性、不存在过擦除问题并且设计简洁。与其他基于浮置栅极(FG)的存储器类似,SuperFlash的耐烧写-擦除次数受烧写和擦除期间电介质层中电子俘获引起的工作窗口关闭的限制。在SuperFlash单元中,擦除和烧写期间会在隧道氧化层和FG氧化层这两个不同的物理位置发生电子转移。这两个区域中俘获的电子会使单元工作窗口在烧写-擦除周期后缩短。了解这两个退化分量的相对贡献对于优化单元的技术和工作条件极其重要。我们提出了一种简单快速的方法,能够分离出SuperFlash单元中循环擦写引起的退化分量。

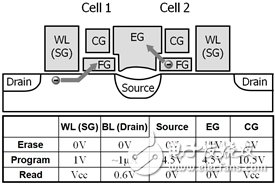

图1 第3代SuperFlash存储单元的结构和典型工作条件。图中给出了两个共用源极和擦除栅极的单元。图中用箭头指示烧写(单元1)和擦除(单元2)期间的电子转移情况。WL为字线(选择栅极),CG为耦合栅极,EG为擦除栅极,FG为浮置栅极。

SuperFlash单元中循环擦写引起的退化分量

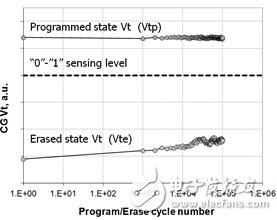

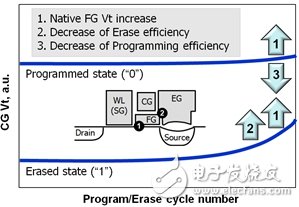

图1给出了第3代SuperFlash单元[3]的结构和典型工作条件。此单元使用源极侧的热电子注入进行烧写,使用针尖增强的多晶硅到多晶硅电子隧穿进行擦除。通常,SuperFlash单元的耐擦写次数受擦除侧工作窗口关闭的限制[4],表现为已擦除状态下单元阈值电压Vte的增大(图2)。本技术中未观察到与单元相关、循环擦写引起的烧写故障:单元在已烧写状态下的Vt(Vtp)保持相对不变,或随循环擦写次数而略微增大。图3给出了主要的循环擦写引发机制,它们负责确定单元"0"-"1"工作窗口的行为。

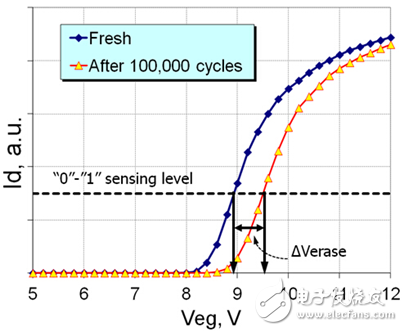

图2 已擦除状态下单元阈值电压(Vte)和已烧写状态下单元阈值电压(Vtp)的循环擦写过程示例

图3 循环擦写引发机制对单元工作窗口的影响

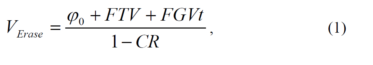

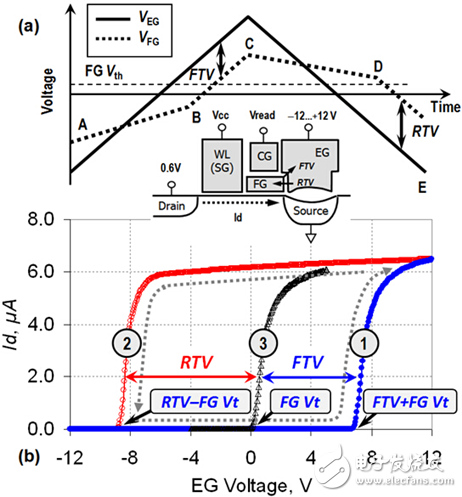

在烧写-擦除循环期间,一些电子被俘获到FG下面的氧化层(FG氧化层)和隧道氧化层中。图3的插图中分别用1和2标出了电子俘获区域的位置。擦除期间隧道氧化层(位置1)中俘获的电子会增加后续隧穿的位垒并降低隧穿效率,这将导致单元的Vte增大[5]。烧写期间FG氧化层(位置2)中俘获的电子对单元的工作窗口具有双重影响。首先,它会使FG"原生Vt"增大,进而使单元的Vte和Vtp都增大。其次,它会降低烧写效率,从而导致Vtp减小。因此,这两种循环擦写引起的电子俘获分量均会导致Vte退化(增大),而Vtp过程则受两个作用相反的机制影响。在擦除电压范围内,烧写-擦除循环导致擦除期间的EG电压(Verase)增大,这是达到特定读取电流值的必要条件,相关示例请参见图4。擦除期间,隧穿电流为常量,Verase等于

图4 循环擦写前和循环擦写后单元的读取电流与擦除电压的关系(累积擦除和固定擦除时间)示例

本文选自《嵌入式技术特刊》,更多优质内容,马上下载阅览

其中,FTV为EG-FG电压差,FGVt为原生FG阈值电压,φ0为读取条件下"超出"FG Vt的FG电势(达到特定读取电流的必要条件);CR为EG-FG电容耦合系数。从(1)可以看出,隧穿电压FTV或FGVt的增大对Verase具有类 似的作用。上述两个擦除退化分量的相对贡献取决于许多因素,包括单元的工作和循环擦写条件、单元的几何形状和工艺过程的参数等。了解主要退化机制对于优化 单元工艺和工作条件非常重要,目的是增加SuperFlash的耐擦写次数。

图5 单元的电容-电阻图及其等效电路

图6 FG电压和EG电压、EG-FG电压差以及流经电阻R的电流的时序图,对应于公式(2)-(4)

方法说明

要分离FG氧化层和隧道氧化层退化对观察到的擦除速度下降情况的影响,需要一个工具来探测循环擦写引起的原生FG Vt的变化,而不是直接测量浮置栅极。如上所示,Vtp或Vte过程中包含多个分量,无法用于得出关于FG Vt变化的可靠结论。早期提出了一种利用经UV照射后的单元的中性状态来监视FG沟道退化状态的方法[6],但这种方法并非始终适用于采用致密金属布局的现代化大规模FG单元;UV擦除还需要特殊的晶圆生产工艺,并可能导致一些电子逃逸,从而影响测量结果。我们提出一种新的快速、非破坏性的电气方法,这种方法基于隧穿电流稳定性在向擦除栅极施加线性斜坡电压时的作用[7,8]。

图7 (a) VEG线性斜坡期间的EG电压和FG电压图;(b) VEG正向变化(曲线1)和反向变化(曲线2)期间测量的单元电流。曲线3显示了在直接接触FG的单元上测量的Id-VFG参考特性(来自[3])。在A-B和C-D区域中,EG-FG电压差小于对应的隧穿电

- 嵌入式系统在电源设计中的运用(09-20)

- 一种小型智能化UPS系统的嵌入式设计方案(09-16)

- 基于无线传感器网络的嵌入式远程测控系统研究(10-17)

- 嵌入式工业以太网控制器的设计和应用(10-17)

- 基于4G通信的嵌入式数据通信系统设计(10-10)

- 嵌入式CPU卡在医用便携式监护仪中的应用及设计(09-23)