FPGA助力智能化人群监控系统

移和常量,从而非常快速地执行所谓的"跨步式"存储器访问。跨步式存储器访问从图像的多行数据访问开始(就如同在 2D 卷积中)。

设计基于 Vivado 的加速器的主要考虑因素是并行处理运动向量的计算,最大限度地提高从主存储器中的数据读取。为此目的,我们使用八个 Block RAM 并行加载和存储视频帧数据。硬件加速器的内核能够并行计算四个运动向量,而且在计算中它会用到所有八个 Block RAM。从主存储器传输到这些 Block RAM 的数据由 MicroBlaze 通过 DMA 加以控制。

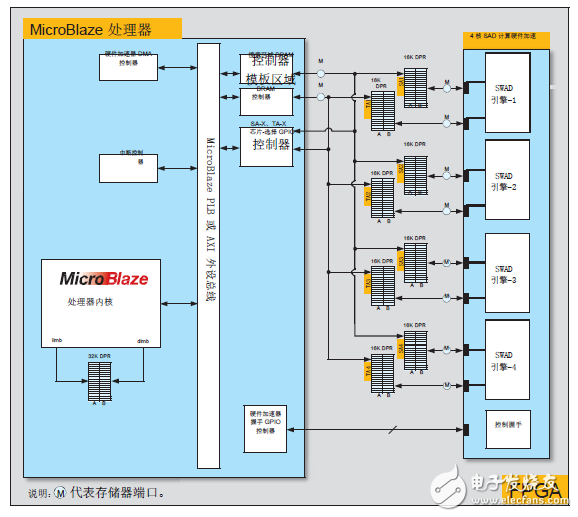

Vivado HLS 生成的硬件加速器具有部分自动生成的握手信号,这些信号对于启停硬件加速器必不可少。 这些握手信号包含"启动"、"繁忙"、"闲置"、"完成"等标志。这些标志通过 GPIO 传送到 MicroBlaze 处理器以完成握手。图 5 所示为该硬件加速器、八个 Block RAM 和 MicroBlaze 处理器主外设总线之间的互联。

图 5:基于 Vivado HLS 的硬件加速器及其互联

图 5 中分别被命名为 SA1、TA1 到 SA4、TA4 的这些 Block RAM,每个的容量为 16KB。每对 SA1、TA1 到 SA4、TA4 能够保存计算一个完整行的运动向量所需的数据。因此硬件加速器在完成运行后,会输出四行运动向量写回到相同的 Block RAM 存储器中。这些计算完的运动向量随即由 MicroBlaze 处理器读回,然后把结果以运动向量网格的形式复制到自己的主存储器中。(图 4 所示的是被硬件加速器计算出的运动向量网格覆盖的实际帧)

该硬件加速器在 200MHz 频率下工作,计算整个图像的运动向量所需的全部处理任务能够在不足 10 毫秒内完成,包括与存储器之间的所有数据往来传输。

算法控制和数据流

在视频流水线和硬件加速器开发就绪后,完成该系统的最后一步是把这两个单元与 MicroBlaze 主机处理器集成,并使用赛灵思软件开发套件 (SDK_,用 C/C++ 实现用户层应用的算法控制和数据流。 在赛灵思 SDK 中实现算法控制和数据流能为设计带来极大的灵活性。这是因为用户可以用相同的方式设计和集成新的硬件加速器,同时还可以修改必要的控制和数据流以集成新的硬件加速器。最终得到的就是一种软件控制、硬件加速的设计,其灵活度可媲美纯软件实现方案,同时其性能可媲美纯硬件实现方案。

本文介绍的人群运动分类算法的控制和数据流从通过视频帧队列 API 功能采集视频帧开始。当视频帧获取完毕,用户应用把当前的和之前的视频帧数据传输到硬件加速器,完成运动向量的计算。

此时系统在软件中计算运动向量的统计属性和分类结果。这样做的原因是这些步骤不涉及任何像素级处理,只会增加很少的处理开销。当分类结果计算完成时,用屏幕显示(OSD)功能把结果和运动向量显示在处理后的帧上。这些屏幕显示功能也是在赛灵思 SDK 中用 C/C++ 语言实现的。

这些构建模块(实时视频流水线、硬件加速器和算法控制/数据流)全部就绪后,总体系统设计即告完成。随后我们对基于 FPGA 的实现方案进行了测试,并与之前的桌面 PC 型实现方案比较结果的准确性。两个结果是完全一致的。我们使用来自明尼苏达大学数据库( http://mha.cs.umn.edu/proj_recognition.sht- ml )和来自www.gettyimages.com 的各种测试视频对本系统进行了测试。

实现方案结果

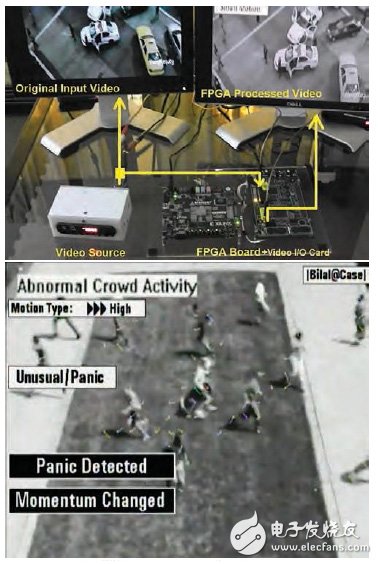

整个设计只使用了 Spartan-6-LX45 FPGA 上 30% 的Slice LUT、60% 的 BRAM 和12% 的 DSP48E 乘法器资源。图 6 所示是硬件设置(上)和实际系统输出。硬件设置由 Digilent Atlys Spartan 6 FPGA 板和定制视频接口卡组成,利用视频 ADC 和 DAC 可为 FPGA 提供视频输入/输出功能。如欲观看该系统的详细演示视频,敬请访问下列 Web 链接:

http://www.dailymotion.com/video/x2av1wo_fpga-based-real-time-hu-man-cro.。.

http://www.dailymotion.com/vid-eo/x23icxj_real-time-motion-vec-tors-comp.。.

http://www.dailymotion.com/video/x28sq1c_crowd-motion-classifica-tion-us.。.

图 6:硬件设置(上)和把场景分类为惊恐的实际 FPGA 处理后的帧

巨大的未来潜力

FPGA 是面向实时视频处理等需要高性能的应用的理想平台。开发这种应用要求进行一定的架构考量,以充分发挥所选 FPGA 的性能优势。此外使用 EDK 和 Vivado HLS 等先进工具,能够以比过去高得多的效率和更短的开发时间实现总体系统设计。

因此正如我们在本文中所展示的,利用上述工具在 FPGA 上实现性能关键型应用有着巨大的潜力。有这样成功运行的平台作为先例,我们期望把这一成果推广用于解决更多的技术问题,例如自动化交通

FPGA 相关文章:

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)

- DE0-Nano-SoC 套件 / Atlas-SoC 套件(10-30)