基于FPGA的8PSK软解调的研究与实现

0 引言

随着卫星通信服务业的发展,人们对服务质量的要求越来越高。2003 年,卫星数字视频广播(DVB-S2)系统采用了高效的低密度奇偶校验码(LDPC),提高了大约30%的带宽效率。众所周知,卫星通信系统中常用LDPC 与BCH 级联的前向纠错编码来获得较高的性能,为了达到这种性能要求,接收信号在解调部分需要使用软解调,因此在高阶调制系统(例如8PSK)中,需要一种合适的,简单易实现的软解调技术来对接收信号进行解映射。在传统的无线通信系统设计中,对数似然比(LLR)算法作为性能最优算法常被用于软判决技术中,然而由于该算法的复杂度过高,涉及到多次对数与指数运算,不适合于硬件实现,因此,很多简化软判算法相继出现。其中最大值(MAX)算法在LLR 算法的基础上简化了指数和对数运算,其硬件实现复杂度与LLR 相比大大降低,同时相比LLR 算法性能损失较小。因此,在通信系统硬件设计中,通常选用MAX 算法作为一种合适的软解调算法对接收信号进行软解调。

这里首先分析了8PSK 软解调算法的复杂度以及MAX算法的基本原理,并在Altera 公司的Stratix II 系列FPGA芯片上实现了此软解调硬件模块,同时与LDPC 译码模块进行了联合验证。通过软硬件验证和分析表明,此设计在运算复杂度、吞吐量、最终误码性能上取得很好的折中。

1 8PSK 软解调原理

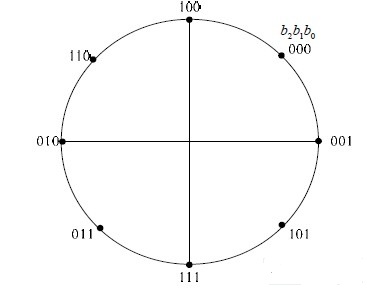

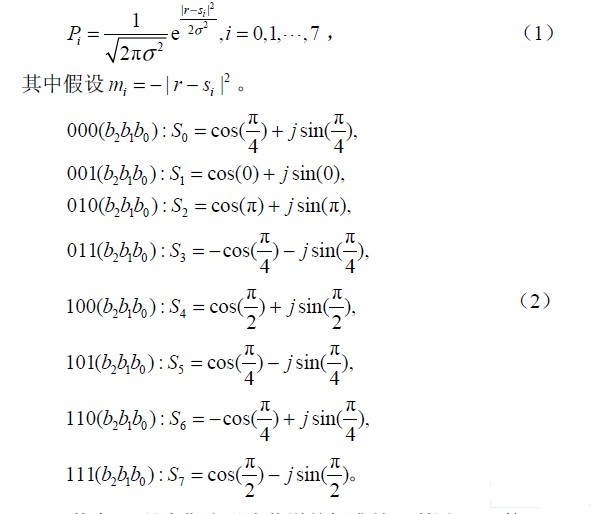

8PSK 的调制星座图如图1 所示,每个符号代表三个比特, 式(1)表示经过高斯白噪声信道后接收信号的概率密度函数,式(2)描述了星座图上每个星座点的值,Si 代表该星座图上1 到8 个星座点。

图1 8PSK 调制星座

其中σ 是高斯白噪声信道的标准差。利用LLR 算法,软判决如式(3)所示,其中分子上的各项表示此比特为0的概率之和,分母各项表示此比特为1 的概率之和。

从式(2)和式(3)可以看出,每计算一比特的LLR,都需要平方、指数和对数运算,因此LLR 算法具有较高的运算复杂度和较大的资源开销,尤其是硬件实现指数、对数复杂度高,所以LLR 算法不适合FPGA 实现。而最大值(MAX)算法能有效避免计算每比特对数似然值的指数和对数运算,其原理如式(4)所示。

由式(3)和式(4)可知,简化以后的MAX 算法如下式(5)所示,对于式(3)和式(5)可知,LLR 算法在硬件上很难实现指数和对数运算,而MAX 算法只需要简单的加减运算和少数乘法运算,易于工程硬件实现,因此选取MAX 算法作为硬件实现的最终方案。

2 算法性能分析

通过MATLAB 仿真平台,做了如下性能仿真对比分析。

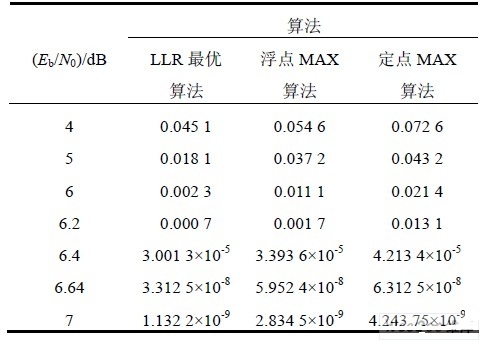

由MATLAB 产生一组随机序列,长度为10 万个编码块,每个编码块为4 032 bit,再经过码率为1/2 的LDPC 编码模块,通过对应的8PSK 调制,在Eb/N0 为4 dB 到7 dB 的区间内,分别经过LLR 最优算法、浮点MAX 算法、定点MAX 算法算出对数似然比,最后分别经过LDPC 译码模块,得出误码性能。

表1 是通过MATLAB 仿真平台计算出来的每个Eb/N0所对应的误码率,图2 是与之相对应的误码率曲线图。由图2 可知,对于Eb/N0 测试区间为4 dB 到7 dB 的任意一个测试点,LLR 最优算法的误码率总比定点MAX 算法和浮点MAX 算法要小,其中浮点MAX 算法误码性能居中,定点MAX 算法最差。MAX 算法是通过降低误码性能来换取运算复杂度的降低,其误码性能要比LLR 最优算法差。与浮点MAX 算法相比,定点MAX 算法对输入软解调模块的I、Q两路信号和输出的似然比分别进行了截位和限幅,如图2 所示,定点MAX 算法相对于浮点MAX 算法损失了一定的误码性能。由表可知,定点MAX 算法在Eb/N0 为6.64 dB 时,其误码率为6.5125×10-8,验证了该定点方案能够满足系统设计要求。

表 1 MATLAB 误码率仿真表

图2 MATLAB 误码率仿真

3 MAX 算法硬件实现

由于硬件实现都是定点运算,所以MAX 算法的实现是针对定点的MAX 算法进行硬件设计的。硬件仿真流图如图3 所示,首先利用MATLAB 产生随机序列,假设每一编码块为4032 bit,LDPC 编码效率为1/2 码率,则经过LDPC 编码后,每一编码块为8 064 bit,经8PSK 调制成符号后,每一个编码块被调制成2 688 个符号,实部虚部分为I、Q 两路,再叠加信噪比为SNR 的高斯白噪声,最后把数据文件存储在RAM 中。在硬件实现上,定点MAX 软解调模块以一定速率从RAM 读取数据并进行软解调,软解调输出的对数似然比存储在乒乓RAM 中,每存满一个编码块就向LDPC 译码器发出一个读有效信号,LDPC 译码器在接收到该有效信号的下一个时钟周期就开始以一定速率读取整个编码块的对数似然值,接着开始进行LDPC 译码,

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)