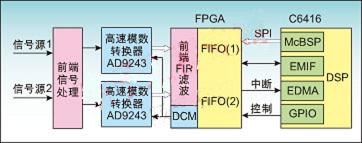

在高速信号采集系统中利用FPGA实现异步FIFO设计

目前数据采集系统朝着高速和高精度的方向发展。随着FPGA|0">

从前面的A/D时序电路中可知,A/D转换数据的输出和转换时钟有一定的相位差,在FPGA内部可通过延时或时钟管理器来满足建立时间和保持时间,保证数据不失码地传输到FIFO中。

2. FIFO与C6416的接口电路

C6416有两个EMIF口,即EMIFA和EMIFB,其中EMIFA的总线宽度支持64b、32b、16b和8b,寻址空间为1024Mb;EMFIB的总线宽度支持16b和8b,寻址空间为256Mb。本文采用EMIFB作为与FIFO的接口,其总线宽度配置为16b。EMIFB可以与各种外部存储器实现无缝接口,如SBSRAM、SDRAM、异步设备(包括SRAM、ROM和FIFO)和外部共享存储设备等。设计中EMFIB和FIFO的接口采用异步读的方式,实现数据的可靠传输,即通过由/ARE和地址来实现对两个同步FIFO的异步读,其控制接口信号的连接关系为:

RD_CLK=/ARE

RD_EN1=A20

RD_EN2=A19

表1:FIFO的输入输出引脚定义

设计中将两个FIFO的存储空间都映射到EMIFB的BCE2中,当FIFO的可编程满信号PROG_FULL有效时,引发外部中断,触发EDMA以实现数据的快速传输。由于FIFO不需要地址线,可以通过简单的接口来产生EDMA的读地址,实现EDMA分时读两个FIFO。异步读FIFO必须满足下列时序关系:

异步读时序如图2所示,其中EMFIB的时钟可以是外部时钟源,也可以是由CPU时钟分频获得。设计中使用外部时钟源,其频率为133MHz,可以根据EMIFB的读写控制寄存器配置Setup、Strobe和Hold的值。

图2:异步读时序图

本文小结

本文系统地介绍了一种由数字信号处理器TMS320C6416、可编程逻辑器件Spartan3E构成的高速数据采集系统。实验表明,系统具有抗干扰强、可靠性高、失码率低等优点。设计中采用了FPGA来构造FIFO,可根据不同的应用场合对FPGA编程以满足设计要求,因此灵活性较大,是一种较好的高速数据采集方案。此外,采用了EDMA传输,适于在实时性要求较高的各种高速数据采集系统中应用。该数据采集卡采用标准扩展总线接口,可以与合众达公司的DEC6000系列开发板连接。

作者:贾龙

开发工程师

truelong@seeddsp.com

北京合众达电子技术有限责任公司

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)