在高速信号采集系统中利用FPGA实现异步FIFO设计

目前数据采集系统朝着高速和高精度的方向发展。随着FPGA|0">FPGA的集成度和运行速度的提高,可以满足高速数据采集系统的需求。FPGA内部具有丰富的存储单元,易于实现各种存储器(如FIFO|0">FIFO、双口RAM等);另外,基于查找表的逻辑单元可用于实现各种数字信号处理(如滤波等),以辅助DSP处理器做各种预处理。

TI公司推出的高性能数字信号处理芯片TMS320C6000系列,工作频率最高可达到1GHz,具有处理速度快、灵活、精确和可靠性高等优点,作为数据采集系统中的主处理器,可以满足实时性的要求。基于以上考虑,北京合众达公司开发了采用TMS320C6416和FPGA的高速高精度双通道数据采集系统,每个通道的采样率为3Msps,最高可达10Msps,采样精度为14b。系统主要包括以下几部分:高速A/D转换、FIFO数据缓存和EDMA数据传输,系统结构框图如图1所示。

AD9243及转换控制

设计中采用的模数转换器芯片是AD9243。AD9243是ADI公司生产的14位、3Msps高性能模数转换器。AD9240与AD9243完全兼容,因此系统的最高采样率可兼容到10Msps。

模数转换器AD9243的时序控制与传统的A/D有所不同,完全依靠时钟控制采样、转换和数据输出,在第一个时钟的上升沿开始采样转换,第四个时钟上升沿到来时,数据将出现在D1~D14端口上。本文采用系统自通电时起,A/D和时钟电路始终处于工作状态,对数据不停进行转换,以减少误码率,提高采样精度。

FIFO的实现及控制

设计中采用FPGA来实现双通道数据的缓存和数据传输的逻辑控制。Spartan3E是一款高性能低价格的可编程逻辑器件,具有丰富的逻辑单元和存储单元。其内部的BlockRam可以配置为大小不同的各种类型存储器,如单口RAM、双口RAM和同步FIFO,其中FIFO更适合作为A/D采样数据高速写入的存储器。FIFO存储器就像数据管道一样,数据从管道的一头流入、从另一头流出,先进入的数据先流出。FIFO具有两套数据线而无地址线,可在其一端写操作而在另一端进行读操作,数据在其中顺序移动,从而达到很高的传输速度和效率,且由于省去了地址线,有利于PCB板布线。

采用FIFO构成高速A/D采样缓存时,由于转换速度较快,如果直接将ADC采样后的数据存储到FIFO中,对时序配置要求非常严格,如果两者时序关系配合不当,就会发生数据存储出错或者掉数。利用FPGA可以方便地控制时序和数据传输,简单、可靠地实现采样和存储是选用FPGA的优点。该数据采集系统中只采用了一个外部时钟源,直接输入到FPGA,经DCM分频后作为FIFO和ADC的时钟源。

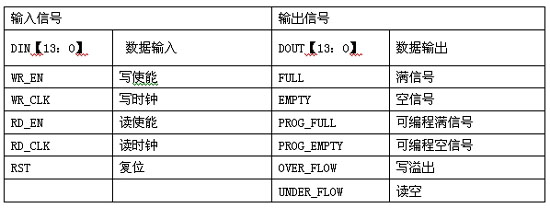

在软件设计中,采用ISE开发环境开发FPGA时,调用Core Generator来构造FIFO,可以设置FIFO的参数,如深度和宽度;设置FIFO的各种标志和控制位,如空满、半满全满、半空全空、可编程满和可编程空等标志位;写使能、读使能等控制位,以便实现与高速A/D和DSP的逻辑接口。FIFO的输入输出引脚如表所示:其中WR_EN由DSP的GPIO口引出,控制数据是否写入到FIFO中,输出引脚中只用到了PROG_FULL即可与DSP进行数据传输。

FPGA的作用除了构造FIFO以实现数据通道复用外,还可以作为协处理器进行实时要求性高的数据预处理(如插值、取平均、FIR滤波等),以减少DSP处理的数据量。设计中采用分布式算法的FIR滤波,首先对ADC转换后的数据进行FIR滤波,然后存入FIFO中以等待DSP的读取。FPGA代替ASIC和DSP作为前端数字信号处理的运算,在规模、重量和功耗方面都有所降低,而且吞吐量更高,开发成本进一步缩小。

FPGA设计中,需提供外部闪存来存储FPGA的下载文件,上电后数据会自动下载到FPGA内部,以对FPGA进行配置。FPGA有多种配置方式,包括主串、从串、主并、从并、SPI、BPI,以及JTAG等方式。串行方式即逐位串行配置,接线简单,但速度比较慢,并行方式即8位同时传输,速度快,但接线复杂。串行方式和并行方式都需要外加闪存作为配置文件的存储器。设计中本文采用C6416的多通道缓存串行口(McBSP)以SPI方式对FPGA进行配置。

图1:系统结构框图

接口和控制电路的设计

系统的接口和控制电路主要包括以下两个部分:

1. ADC与FIFO的接口电路

利用FPGA构造了两个完全一样的FIFO,将两路A/D转换数据分别送入两个FIFO中,实现双通道采样数据的缓存和传输。设计中A/D转换时钟和FIFO写时钟为同一时钟源,自上电起,A/D和时钟电路一直处于工作状态,不停的进行数据的转换,但数据是否写入到FIFO中,由FIFO的写使能信号来决定,当DSP发出写使能信号有效时,转换数据才能存储到FIFO中。

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)