汽车显示器架构中的外部和内部接口及其整合选型

引言

现在大型面板LCD市场(LCD电视、桌面PC监视器、笔记本电脑监视器)正在朝着高度标准化和整合化迈进,而汽车信息娱乐LCD架构踯躅在传统的概念中。主要原因在于业界通常倾向于购买完整的LCD模块,而将精力集中在视频适配器或接口卡设计上。现在,采用基本TFT玻璃以及加入差异化设计的显示器的定时控制器(TCON)正在成为新潮流。除了外部LCD接口外,还可以考虑内部显示接口,例如现在的工业标准RSDS( 抑制摆幅差分信号)总线技术。内部和外部接口的整合的益处真是举不枚举:所用元件更少、节约PCB空间并降低EMC辐射和磁化效益。此类收益也适用于图像主控应用,该应用一般发生在一个汽车音响本体ECU(电子控制单元)内。现在的图像处理单元(GPU)正逐渐弃用宽CMOS/TTL输出,因为它会消耗大量的封装引脚。目前,越来越多的图像源元件可提供根据串联数据通道而成的第一级串联化,以供带有并联时钟通道的色彩位应用。参照开放的工业标准"FPD-Link"物理层的规定,预计未来还会进一步提高连接选择的灵活性。这样,第一级的串联化可通过采用桥接芯片来获得升华,从而在单一对的互连上提供第二级串联化,以便产生出纤薄和可连到很远的电缆连接方案,这对汽车外壳布线--特别是要连接到后座娱乐显示器的应用-尤其重要。

传统的图像与远程LCD面板连接

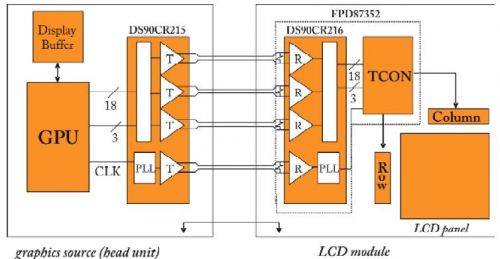

在传统的汽车信息娱乐系统设计中,图像控制器或图像处理单元(GPU)会传送有图素时钟和同步信号对齐的并联RGB颜色位。如图1中所示。在远程的LCD显示器连接中,有时会因缆线太厚,或电源和EMC(电磁兼容性)等的问题而导致并联总线不能跨越超过20-30厘米的长度。针对这个问题,美国国家半导体在90年代的中期与当时领导业界的TFT面板供应商一起研发了崭新的串联/解串(SerDes)FPD-Link(平面显示器--链接)芯片组系列。该传送器接受高至18位的RGB信息(6位色彩深度模式)以及三个控制信号和时钟,然后将它们转换成三个差分数据对和一个时钟对。在面板上设置了补足功能。FPD-Link接收器将数据流反串联化,并且把图素数据和控制信号提供给面板上的TCON(定时控制器),接着它会将信号重新格式化并路由到LCD玻璃的行和列驱动器。FPD-Link物理层的位映射和信号格式已成为SPWG(标准面板工作小组)订立的标准并成为笔记本电脑LCD监视器的工业标准连接方案。该芯片组采纳LVDS(低压差分信号)物理层的标准:ANSI/TIA/EIA-644A。LVDS是一个高速兼低功耗的接口,它不单被应用到时下的嵌入式显示器,而且还可应用在要求高速数据传输的各式各样数据通信和电传通信上。它的优点包括可提供速度很高的线传输率、功耗较少,以及所产生的噪声较低和非常耐用。此外,它在排除共模噪声方面的能力,比起真正的差分信号强一倍。如此一来,高分辨率的面板可经由较小的接口支援,从而简化了互连上的设计,同时仍可支援各级的面板分辨率。FPD-Link的概念还可引伸到更全面的"OpenLDI" (LVDS显示器接口)规格。OpenLDI详细描述出显示器源和传送数字显示器数据的显示器件之间的接口逻辑、电气和机械特性。对于超过10米的长程线接应用,可以采纳LVDS SerDes的强化版本。包含在传送器内的强化部份是可自选预加重和一个简单的低功耗直流平衡方案,以在冗长缆线的未端打开眼图。另外,接收器还提供缆线反偏斜功能,可允许使用标准的双纹线。在其"LVDS非直流平衡"模式中,OpenLDI物理层能够逆向兼容,而且与FPD-Link物理层一模一样。

四线道和单线道串联/反串联转换器之间的LVDS桥接概念

现在有越来越多的图像处理器、定标器和甚至是中低档的FPGA都整合有FPD-Link物理层。整合主要优势在于可以在多条受限中速数据通道上分发大数据流,并可减低在复杂数字芯片内采用高频锁相环路(PLL)和时钟数据恢复(CDR)电路的设计风险。另一方面,在汽车外壳的布线上,四线道(八条缆线)差分互连所产生出来的缆线仍相对较厚和灵活性也较低。长度超过5米的缆线可能会因缆线的构造和规格而在数据和时钟通道间产生潜在的偏斜问题。在汽车的安装过程中,由于制造商倾向采用交流耦合连接以便为传送和接收端上的位移接地电位提供隔离,因此更合乎逻辑的方案是包含有嵌入式时钟方案的单线道转换方案。对于设有FPD-Link接口的图像源来说,美国国家半导体出品的DS99R421可以把四条非直流平衡式的LVDS 线道(三条 LVDS数据加一条LVDS时钟)连同三个过取样的低速控制位 (OS<2:0>现在有越来越多的图像处理器、定标器和甚至是中低档的FPGA都整合有FPD-Link物理层。整合主要优势在于可以在多条受限中速数据通道上分发大数据流,并可减低在复杂数字芯片内采用高频锁相环路(PLL)和时钟数据恢复(CDR)电路的设计风险。另一方面,在汽车外壳的布线上,四线道(八条缆线)差分互连所产生出来的缆线仍相对较厚和灵活性也较低。长度超过5米的缆线可能会因缆线的构造和规格而在数据和时钟通道间产生潜在的偏斜问题。在汽车的安装过程中,由于制造商倾向采用交流耦合连接以便为传送和接收端上的位移接地电位提供隔离,因此更合乎逻辑的方案是包含有嵌入式时钟方案的单线道转换方案。对于设有FPD-Link接口的图像源来说,美国国家半导体出品的DS99R421可以把四条非直流平衡式的LVDS 线道(三条 LVDS数据加一条LVDS时钟)连同三个过取样的低速控制位 (OS<2:0>)转换成单一条具有嵌入式时钟信息的LVDS直流平衡式串联数据流,如图2所示。这种串联化方案由于消除了在数据和时钟路径间的偏斜,故此

- 汽车影音系统的图像处理器的应用(08-03)