一文读懂集成扇出型封装(InFO)技术

集成扇出型封装(InFO)技术是什么?作为目前移动市场最受欢迎的技术,为什么目前只有两家公司能够生产,其中的难点是什么?

晶圆代工大厂格芯于2017年8月 15 日宣布,采用高效能 14 纳米 FinFET 制程技术的 FX-14 特定应用积体电路(ASIC)整合设计系统,已通过 2.5D 封装技术解决方案的矽功能验证。

目前,全由晶圆代工大厂中,仅台积电拥有集成扇出型封装(InFO)技术,速度效能较传统的覆晶技术要高 10%,让台积电在市场竞争上具备竞争实力。如今,格芯也成功进入先进晶圆封装的领域,成为全球唯二拥有这类技术的厂商,将进一步增加市场的竞争优势。

集成扇出型封装(InFO)技术是什么

说到InFO技术,就不得不提到FOWLP。

Fan Out WLP的英文全称为(Fan-Out Wafer Level Packaging;FOWLP),中文全称为(扇出型晶圆级封装),其采取拉线出来的方式,成本相对便宜;FOWLP可以让多种不同裸晶,做成像WLP制程一般埋进去,等于减一层封装,假设放置多颗裸晶,等于省了多层封装,有助于降低客户成本。此时唯一会影响IC成本的因素则为裸晶大小。

DIGITIMES Research观察,系统级封装(System in Package;SiP)结合内嵌式(Embedded)印刷电路板(Printed Circuit Board;PCB)技术虽符合移动设备小型化需求,然于供应链与成本存在问题,另一方面,扇出型晶圆级封装不仅设计难度低于矽穿孔(Through Silicon Via;TSV) 3D IC,且接近2.5D IC概念与相对有助降低成本。

FOWLP封装最早在2009~2010年由Intel提出,仅用于手机基带芯片封装。

2013年起,全球各主要封测厂积极扩充FOWLP产能,主要是为了满足中低价智慧型手机市场,对于成本的严苛要求。FOWLP由于不须使用载板材料,因此可节省近30%封装成本,且封装厚度也更加轻薄,有助于提升晶片商产品竞争力。

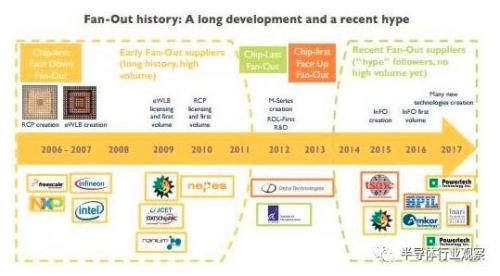

台积电(TSMC)在扇出型晶圆级封装领域投入并开发了集成扇出型(Integrated Fan-Out, InFO)封装技术,改变了晶圆级封装的市场格局。随着InFO技术的大规模应用,以及嵌入式晶圆级球栅阵列(eWLB)技术的进一步发展,一批新厂商和扇出型晶圆级封装技术可能将进入市场。台积电的扇出型晶圆级封装解决方案被称为InFO,已用于苹果iPhone 7系列手机的A10应用处理器封装,其量产始于2016年。

台积电在2014年宣传InFO技术进入量产准备时,称重布线层(RDL)间距(pitch)更小(如10微米),且封装体厚度更薄。

InFO给予了多个芯片集成封装的空间,比如:8mm x 8mm平台可用于射频和无线芯片的封装,15mm x 15mm可用于应用处理器和基带芯片封装,而更大尺寸如25mm x 25mm用于图形处理器和网络等应用的芯片封装。

2016年可以说是扇出型封装市场的转折点,苹果和台积电的加入改变了该技术的应用状况,可能将使市场开始逐渐接受扇出型封装技术。扇出型封装市场将分化发展成两种类型:

- 扇出型封装"核心"市场,包括基带、电源管理及射频收发器等单芯片应用。该市场是扇出型晶圆级封装解决方案的主要应用领域,并将保持稳定的增长趋势。

- 扇出型封装"高密度"市场,始于苹果公司APE,包括处理器、存储器等输入输出数据量更大的应用。该市场具有较大的不确定性,需要新的集成解决方案和高性能扇出型封装解决方案。但是,该市场具有很大的市场潜力。

扇出型封装的挑战

虽然FOWLP可满足更多I/O数量之需求。然而,如果要大量应用FOWLP技术,首先必须克服以下之各种挑战问题:

(1) 焊接点的热机械行为: 因FOWLP的结构与BGA构装相似,所以FOWLP焊接点的热机械行为与BGA构装相同,FOWLP中焊球的关键位置在硅晶片面积的下方,其最大热膨胀系数不匹配点会发生在硅晶片与PCB之间。

(2) 晶片位置之精确度: 在重新建构晶圆时,必须要维持晶片从持取及放置(Pick and Place)于载具上的位置不发生偏移,甚至在铸模作业时,也不可发生偏移。因为介电层开口,导线重新分布层(Redistribution Layer; RDL)与焊锡开口(Solder Opening)制作,皆使用黄光微影技术,光罩对準晶圆及曝光都是一次性,所以对于晶片位置之精确度要求非常高。

(3) 晶圆的翘曲行为: 人工重新建构晶圆的翘曲(Warpage)行为,也是一项重大挑战,因为重新建构晶圆含有塑胶、硅及金属材料,其硅与胶体之比例在X、Y、Z三方向不同,铸模在加热及冷却时之热涨冷缩会影响晶圆的翘曲行为。

(4) 胶体的剥落现象: 在常压时被胶体及其他聚合物所吸收的水份,在经过220~260℃迴焊(Reflow)时,水份会瞬间气化,进而产生高的内部蒸气压,如果胶体组成不良,则易有胶体剥落之现象产生。

此外,市场的发展也给FOWLP封装技术带来了一定的挑战。

根据麦姆斯咨询的一份报告显示。尽管扇入型封装技术的增长步伐到目前为止还很稳定,但是全球半导体市场的转变,以及未来应用不确定性因素的增长,将不可避免的影响扇入型封装技术的未来前景。

随着智能手机出货量增长从 2013 年的 35% 下降至 2016 年的8%,预计到 2020 年这一数字将进一步下降至 6%,智能手机市场引领的扇入型封装技术应用正日趋饱和。尽管预期的高增长并不乐观,但是智能手机仍是半导体产业发展的主要驱动力,预计 2020 年智能手机的出货量将达 20 亿部。

- 18寸晶圆量产时间再后延(02-28)

- 科学家发明新技术 可让手机充一次电使用数月(03-15)

- ST-Ericsson 推出PowerHUB移动设备充电解决方案(04-08)

- 晶体管进入3-D时代!(05-06)

- 6家企业加入3DIC芯片堆叠技术启动项目(05-03)

- 22纳米到底如何小而强大?(05-06)