深度学习硬件这件事,GPU、CPU、FPGA到底谁最合适?

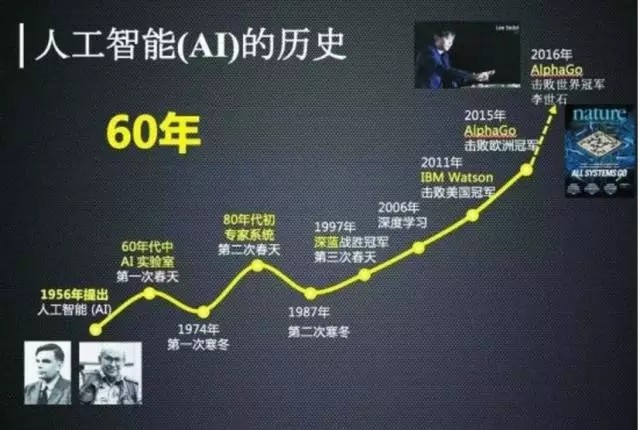

去年3月的那场人机大战,不仅让谷歌的人工智能"AlphaGo"一炮走红,也让它背后的深度学习(Deep Learning)这个概念为公众所熟知。回顾人工智能的发展史,我们发现深度学习并不是一个新兴的概念,早在80年代末期,Geoffrey Hinton和Yann LeCun等学者就提出深度学习的方法并且解决了手写体数字的识别问题。但是遗憾的是,进入90年代后,一方面受限于对于此套理论的认识不完全和当时硬件低下的计算能力,再者业界纷纷开始追逐摩尔定律所带来的红利,深度学习的风潮随之沉寂下去。

然而,伴随着摩尔定律带来的芯片计算能力和存储能力大幅提升和大数据时代的来临,一个"深度学习+大数据"的模型组合将人工智的研究能推向了一个新的高潮。诚然,深度学习的核心驱动力是算法:利用算法/函数去模仿和逼近人脑思维方式。而这些算法/模型最终还是要依赖高性能的硬件来实现对于数据的处理。说起关于计算机数据处理的硬件。毫无疑问CPU是第一个被大家联想到的。 但是在深度学习的世界里,CPU并不是一个最佳的选择。好马配好鞍,今天,我们就来聊一聊深度学习中的硬件。

一、深度学习对硬件的需求

一般来说,深度学习包含两个阶段:数据训练和推断。

在数据训练阶段,大量的标记或者未标记的数据被输入深度神经网络中进行监督或者无监督的学习。所谓监督学习,就是输出是有标记的学习,让模型通过训练,迭代收敛到目标值;而非监督学习不需要人为输入标签,模型通过学习发现数据的结构特征。从而使机器能够在大数据中提取更多的特征值。在最近的《最强大脑》中,百度的机器人"小度"展示了强大的识别能力,据百度首席科学家吴恩达透露,在声纹识别任务中"小度"所使用的神经网络是在大约 5000 多小时的音频数据基础上训练出来的。这亿万级的参数、千亿的样本和千亿特征训练使得神经网络对于语音识别变得相当准确。

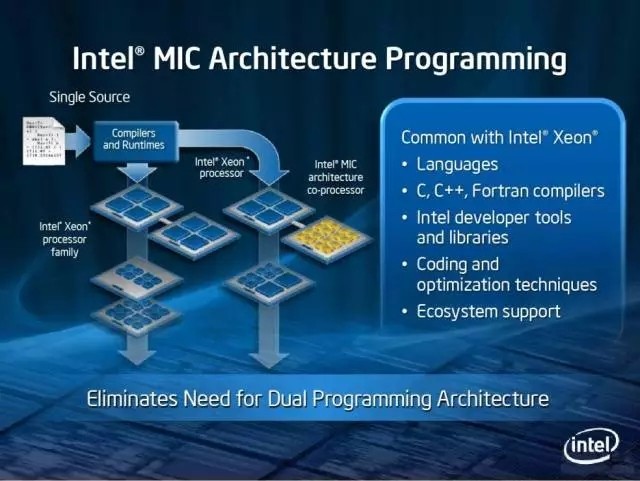

随着深度神经网络模型层数的增多,与之相对应的权重参数成倍的增长,从而对硬件的计算能力有着越来越高的需求,尤其是在数据训练的阶段。因此,深度学习训练领域的前沿逐渐从算法转移到了对于高性能计算(HPC)的追逐上。目前被业内广泛接受的是"CPU+GPU"的异构模式和"MIC (Many Integrated Core)"众核同构来实现高性能计算。

推断阶段就是利用训练中所获得的特征值去对新的输入数据进行判断或者预测。从应用上来说,推断可以分为两大类:线上数据中心的推断和移动设备中的推断。

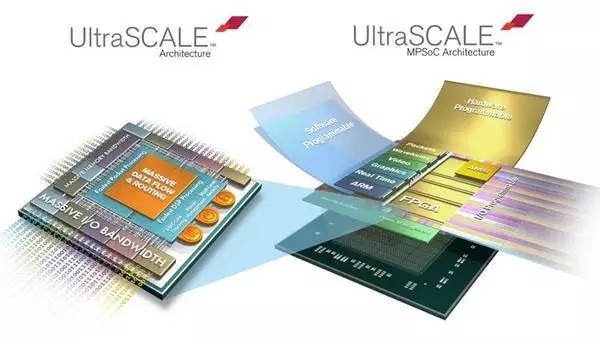

相较于训练阶段执着于对高性能计算的需求,线上数据中心的推断不仅要求硬件有着高性能计算,更重要的是对于多指令数据的处理能力。就比如"Bing"搜索引擎同时要对数以万计的图片搜索要求进行识别推断从而给出搜索结果。目前而言,"CPU+GPU"的异构模式依旧是第一选择,但是"CPU+FPGA"异构计算已经显示出他在这方面的潜力。

而移动设备中的推断更强调在高性能计算和低功耗中寻找一个平衡点。在这个领域的深度学习的执行还是更多的依赖于"CPU+FPGA"与"ASIC"。

二、数据的训练:CPU与GPU之争

2.1、现状

在如今的深度学习平台上,CPU面临着一个很尴尬的处境:它很重要又不是太重要。 它很重要,是因为它依旧是主流深度学习平台的重要组成部分:现百度首席科学家吴恩达曾利用16000颗CPU搭建了当时世界上最大的人工神经网络"Google Brain"并利用深度学习算法识别出了"猫",又比如名震一时的"AlphaGo"就配置了多达1920颗CPU。

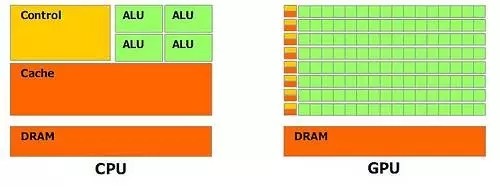

但是它又不是太重要:相比于其他硬件加速工具,传统的CPU在架构上就有着先天的弱势。

上图是CPU与GPU内部结构上的对比,总体上来说二者都是由控制器(Control),寄存器(Cache、DRAM)和逻辑单元(ALU:Arithmetic Logic Unit)构成。但是三者的比例却有很大的不同。在CPU中控制器和寄存器占据了结构中很大一部分,与之相反,在GPU中,逻辑单元的规模则是远远超过其他二者之和。这种不同的构架就决定了CPU在指令的处理/执行,函数的调用上有着很好的发挥,但由于逻辑单元所占比重较小,相对于GPU而言,在数据的处理方面(算术运算或者逻辑运算)的能力就弱了很多。

我们拿NIVIDA公司基于Maxwell构架的GPU来详细说明。这颗代号GM200的显示核心主要由4个图形处理集群(GPC:Graphics Processing Clusters ),16个流处理集群(SMM:Steaming Multiprocess)和4个64bit显存控制器组成。每个流处理集群中包含了4个调度器(Warp),每个调度器又控制着32个逻辑计算核心(Core),这些Core是实现逻辑计算的

- 国内电子阅读器销量破百万 冲破发展瓶颈关键在内容(02-22)

- 台湾移动互联遇短板:硬件厂商大陆抢人才(06-07)

- 芯片大厂加入低价竞争 未来芯片市场愈发激烈(12-21)

- 移动支付之争剑拔弩张:硬件成本成普及拦路虎(01-11)

- 半导体消费无线硬件商居首 超普通PC厂商(02-06)

- 2012 MWC初探 华为大放异彩(03-05)