从IC设计到嵌入式系统的发展

Mentor:不仅EDA,更提出嵌入式软件自动化(ESA)

Mentor Graphics公司最近有了新定位,不再是EDA厂商的代表了,而是EDA和嵌入式软件厂商。

在9月2日北京举行的Mentor年度大会--EDA Tech Forum2010上,该公司董事长兼CEO Wally Rhines从IC设计业的状况开始分析,带我们一步步发现ESA的价值。

IC设计业的未来

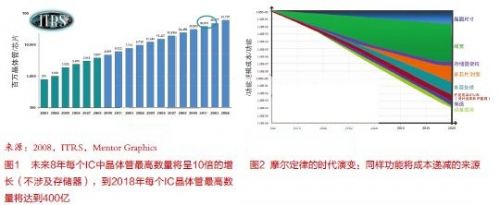

预计IC业将有10倍设计增长需求,8年后的2018年,一块芯片中将有400亿晶体管;12年后的2022年,一块芯片中将有1000亿个晶体管(图1)。这1000亿不涉及存储器(存储器现已达到1000亿晶体管规模),主要指逻辑+存储等。

摩尔定律能否带我们达到1000亿晶体管目标?业界普遍认为不太可能,仅减小晶体管制造的特征尺寸已经不够了。我们必须要采用其他办法,例如多层(2D)封装、3D封装等。如图2所示摩尔定律的时代演变,是在同样功能时将成本递减的主要来源。半导体业与其他工业不同,从数量来看,半导体工业是持续增长的一个行业,每年晶体管数量增49%,芯片数量增13%,但每个晶体管成本年降低35%左右。预计即使在摩尔定律过时多日之后,即超越摩尔时代,每年的晶体管数量仍将持续递增,芯片每项功能的成本仍将持续降低。

近年来,半导体企业改组(重组、分化)现象也频繁,可见半导体业的演变十分剧烈,但实际上大企业在整个半导体业的市占率没有变得更高,而是越来越低,即大公司变小了(表1)。如果观察5年前、10年前、20年前、30年来第一名和前十大、二十大在整个半导体行业的比重,会发现这样的趋势,而且多年前的前十大有的已不是现在的前10名,一些企业甚至已消失了。

对中小企业而言,由于上亿门设计不是每家设计公司可以负担得起的。所以50%初创公司做数模混合或射频及纯粹的模拟IC等,因为投资小,需要专门的技巧,只要找到模拟秘诀就可以做。而大型企业往往做复杂的大规模设计。

ESA(嵌入式软件自动化)将向EDA工具一样普及

那我们如何设计400亿晶体管的芯片?好消息是尽管很难,但设计师门一直采用革命性的设计方法,从1988年开始EDA(电子设计自动化)设计工具(图3),到现在已经发生了巨大的技术变革。当前,400亿晶体管IC所需要的EDA工具可能已经存在了,但我们不能依靠目前的设计工具来设计1000亿只晶体管。下一步,我们要靠四个方面的创新:系统级设计、功能验证、物理设计与验证、嵌入式软件。

按照目前的设计模式,SoC设计成本预计在三年内超过1亿美元。但嵌入式软件也很重要(图4),因为预计设计成本仍在持续增长,其中大多数是用于软件。今天超过一半的芯片设计团队中一半是软件工程师。因此Mentor Graphics预测就像1980、1990年代做EDA(电子设计自动化)工具一样,嵌入式软件自动化(ESA)将会得到大力发展。ESA将使嵌入式系统软件开发和验证自动化,就像EDA工具做IC设计一样。其实,复杂IC今天需要系统软件的支持,例如台湾联发科技和展讯不仅提供芯片,连软件也一并提供,说明了ESA的重要性。

Mentor Graphics公司认为ESA主要有三个方向:⒈增加设计复用,例如Mentor现在已经有工具来允许你用标准的嵌入式软件,更快速地做嵌入式设计应用;⒉生态环境和平台,开发平台像AutoSAR、Executable UML(xtUML),Matlab可用于软件开发;⒊开放标准,像Linux和Android等,这些开放源码为下一代产品作贡献。

值得一提的是,嵌入式标准化可以把设计门槛降低,让更多的人做有创意的界面。例如苹果公司的产品并没有什么了不起的技术,而是把界面做得大家非常喜欢。其实在这些界面以下是一些可以标准化的东西。关键是你想到这个创意,把这个内容丰富、易用、有吸引力,这才是做差异化、增加价值的所在。

处理器+FPGA或将是性能提升的良策

在处理器领域,也面临着性能的挑战

不久前,Altera在京宣布通过新系统级集成工具,针对嵌入式系统配置功能启动嵌入式计划。其FPGA设计流程将支持基于ARM、Intel、MIPS体系结构多种嵌入式处理器产品。Altera产品和企业市场副总裁Vince Hu专程来京,他从业界需求的角度,阐述了处理器+FPGA将带来的巨大能力(如图5)。

首先,对更高软件性能的需求持续增长。而在五年前业界就开始朝系统处理并行化方向发展,而不是仅仅提高单个CPU核的性能。这种并行化的方向主要包含两类技术,一种是多内核,第二种就是硬件协处理加速器。

硬件协处理加速器是较理想的或者效果较好的。但是没有任何的方式能够提前知道哪些软件功能需要通过硬加速的方式实现。所以FPGA是较理想的加速器的实现方案之一,因为它是现场可编程的。但是为了使FPGA协加速,达到理想的性能和效率

- 嵌入式系统与FPGA的最新动向(05-18)

- 有效利用巨量资料智慧型嵌入式系统备受瞩目(10-23)

- 意法半导体在ESC 2010上展示最新最强的嵌入式系统技术 (03-28)

- 也许单片机不再需要调试接口引脚(04-11)

- 交流、设计、实现,ADI在线设计峰会半程盘点(10-19)

- 嵌入式系统需求递增 ADI再遇市场良机(03-14)