100MHz 数字存储示波表样机的研究与试制----数据采集系统设计(二)

11.

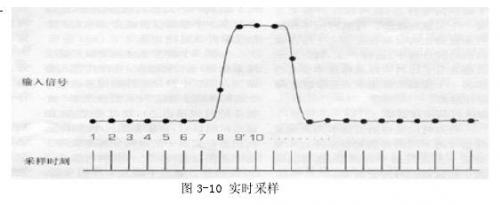

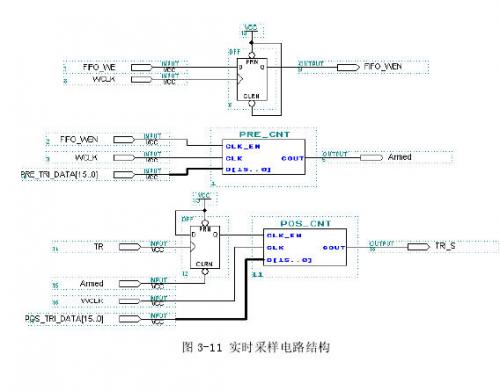

首先,在每个写时钟(WCLK)检查DSP是否发出FIFO写使能信号(FIFO_WE)。当检测到写使能信号,FIFO写使能(FIFO_WEN)有效,前置计数器PRE_CNT(相当于3.3.3节的INT2计数器)根据预先设置好的预触发深度,按照写时钟计数。此时,FIFO只有写时钟有效。当预触发满后,允许触发信号(TR)。在等待触发的过程中,FIFO读时钟等于FIFO写时钟。当触发信号到来,则使能后置计数器POS_CNT(相当于3.3.3节的INT1计数器)根据预先设置好的延迟触发时

间,同样按照写时钟计数。当计数结束后发出TRI_S信号关闭FIFO读时钟,使FIFO只写不读直到FIFO写满,完成一次数据采集。注意,前置计数器PRE_CNT和后置计数器POS_CNT里的计数值分别代表触发点位于屏幕内外时距屏幕最左端的距离,所以,这两个计数器不会出现同时置数的情况。

2.实时采样的显示

当FIFO里数据采集满以后,就要将数据读回显示。由于本系统设计的存储深度为2.5K,而显示屏时间轴上的点数为250,所以显示时要将采集的数据抽点显示,即将每10个点当中的两个点显示在同一个时间轴上,其中一个为最大点,一个为最小点。波形显示有点显示和连线显示两种方式。点显示方式下,将2.5K FIFO的数据读回以后,每隔10个点中取出最大值和最小值,然后显示在同一时间轴上。当在连线方式下时,则要将前一个时间轴上的最大最小值和后一个时间轴上的最大最小值相比较,根据比较结果将点连线显示。

由于AD采集的数据是8位,即取值范围在0~255之间,而LCD上的幅度轴上只有200个点。这样必须要将采集的数据作相应的处理。即若数据小于28的,在显示屏上作0处理,大于228的作200处理,其他的数据都减去28后作显示的数据。这样保证了所有的采集的数据都在波形显示区了。

3.4.2顺序采样

顺序采样是一种等效时间采样,它不是在一个信号周期内捕获全部的采样点,而是每个信号周期只捕获一个采样点。当第一个触发事件到来以后就立即采集第一个采样点,存入存储器。第二个触发事件到来后,由一个定时器产生一个很小的时间延迟△t,经过这个△t的延迟时间以后再采集第二个采样点。第三个触发事件到来后,该定时系统则产生2△t的延迟时间。此延迟时间过后再采集第三个采样点,并这样进行下去。这就是说第n个新的采样点的采集是在相对于相同触发事件延迟了(n-1)△t的时间以后进行的。其结果是示波器上显示的波形是由按固定次序出现的采样点构成的。即第一个采样点在屏幕的最左边,接着各采样点依次向右构成显示波形(如图3-12)。在顺序采样模式下,采集波形的周期数,即触发事件数等于所捕获采样点的个数。顺序采样可以实现"+"延迟触发,但由于它的采样都发生在触发事件后,所以顺序采样不能提供预触发信息。本项目中没有采用顺序采样技术,所以在这里只对顺序采样做概念性的介绍。