100MHz 数字存储示波表样机的研究与试制----DSP 芯片的连接与配置(二)

4.3存储空间的分配

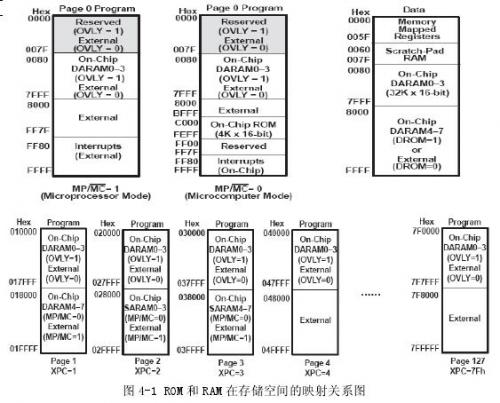

TMS320VC5416的存储空间分为三个部分:程序空间、数据空间、I/O空间。这三个地址空间的总寻址范围为192K.由4.1节的介绍我们知道TMS320VC5416片内驻有16KW的ROM和128KW的RAM.它们在程序空间和数据空间的映射关系如图4-1.

由图我们可以看到,当MP/MC=0时,16KW的ROM映射到程序存储空间地址为C000h~FFFFh空间。DARAM0~3驻留在数据空间的0000h~7FFFh.当OVLY=1时,DARAM0~3映射到程序空间每一页的0000h~7FFFh,即访问程序空间每一页的0000h~7FFFh地址时,相当于是访问数据空间的DARAM0~3.DARAM4~7驻留在程序空间的018000h~01FFFFh,当DROM=1时,其映射到数据空间地址为8000h~FFFFh空间。程序与数据空间的相互映射可以减少存储空间之间数据的相互调用,从而缩短指令的执行时间,提高程序的运行效率。SARAM0~3驻留在程序空间第二页的028000h~02FFFFh,SARAM4~7驻留在程序空间第三页的038000h~03FFFFh.它们都作为程序空间的一部分。

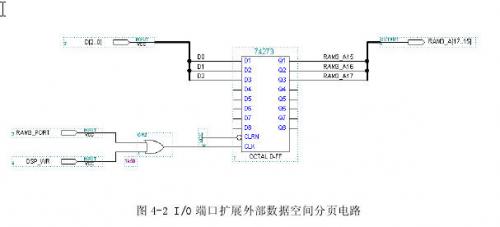

在本项目中,我们用512K×16Bit的Flash作为DSP的片外程序存储空间扩展,总线16位,用于16位方式的并行引导装载和数据保存。其中既保存了用户主程序、模拟Bootloader等程序,还保存了数据:如中英文字库、DSO波形数据、设置等。另外,我们还用256K×16Bit的外部RAM作为DSP的片外数据存储空间的扩展。这256K RAM通过I/O扩展(如图4-2)分为8页,每页32K.当要访问数据存储空间的高32K地址(8000h~FFFFh)时,可以根据RAM3_A[17..15]的值,选择不同的页去对应数据存储空间的高32K.

在硬件设计中,我们用VHDL语言编写分配了程序和数据空间地址。部分程序代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ENCODE IS

PORT(DSP_A[22..16]:IN STD_LOGIC_VECTOR(6 DOWNTO 0);

DSP_PS,DSP_DS,A15:IN STD_LOGIC;

FLASH_CS,RAM_CS : OUT STD_LOGIC;

);

END ENTITY;

ARCHITECTURE BEHAV OF ENCODE IS

BEGIN

A:PROCESS(DSP_A[22..16],DSP_PS)

BEGIN

IF(DSP_PS='0' ) THEN

IF(DSP_A=0 and A15='1') THEN

FLASH_CS<='0';

ELSIF(DSP_A=8 and A15='0')THEN

FLASH_CS<='0';

ELSIF(DSP_A>8 and DSP_A<=15)THEN

FLASH_CS<='0';

ELSE

FLASH_CS<='1';

END IF;

ELSE

FLASH_CS<='1';

END IF;

IF(DSP_DS='0' AND A15='1') THEN

RAM_CS<='0';

ELSE

RAM_CS<='1';

END IF;

END PROCESS A;

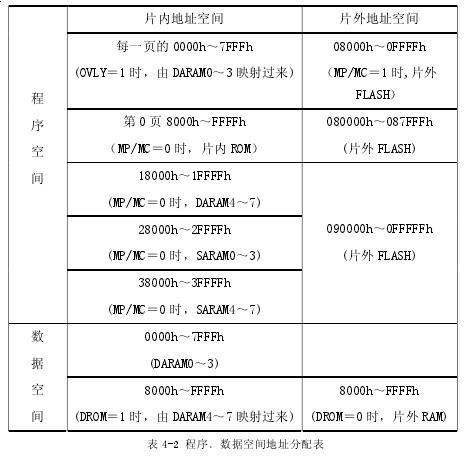

从以上程序以及结合图 4-1,我们可以得到程序和数据空间的地址分配如表4-2。

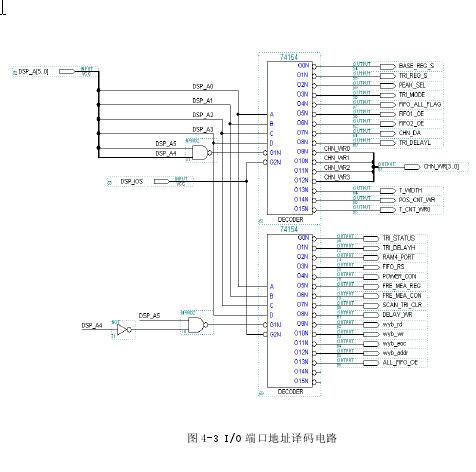

I/O空间也就是I/O端口地址译码,它主要是通过DSP的IOSTRB信号和DSP地址信号的配合译码地址,使之产生相应操作的控制信号。如:时基选择控制,预触发控制,FIFO读写控制,峰值检测功能选择等等。它的具体电路实现如图4-3.

第五章显示控制电路

随着通信、IT与多媒体市场的兴起,耗电少、辐射低,易于携带的液晶(LCD)(liquid crystal display)成为手持仪器的首选。与CRT相比,液晶具有以下优点:

◇低功耗。极低的工作电压,只有3-5V,工作电流在几个UA/(cm)*2.因此液晶显示可以和大规模集成电路直接匹配,使便携式电子计算机、电子仪表成为可能。

◇平板型结构。液晶显示基本结构是由两片玻璃组成的夹层盒。这种结构的优点,一是在使用上最方便,无论大型,小型,微型都很实用。

◇被动显示型。液晶显示本身不发光而是靠调制外界光进行显示。

◇显示信息量大。与CRT显示相比,液晶显示没有荫罩限制,像素可以做得很小,这对于未来的高清晰度电视。是个理想的选择方案。

◇易于彩色化。液晶彩色化,非常容易,方法也很多,更可贵的是液晶的彩色是可以在色谱上非常准确的复现,因此,不会产生色失真。

◇液晶显示工作时,没有电磁辐射。

◇长寿命。这种器件本身几乎没有什么劣化问题。因此寿命极长。

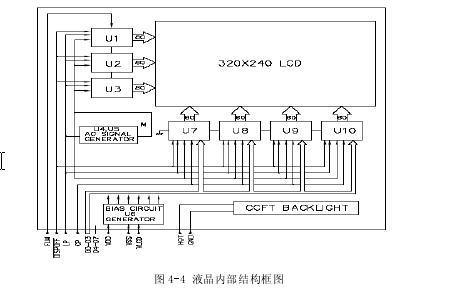

本项目中,我们选用了NANYA公司型号为LTBHB203E1K的黑白显示屏。它是320×240点阵的LCD.内部结构如图4-4所示。

一般LCD显示都采用专用的液晶显示控制模块,实现屏幕分割,屏幕逻辑运算等复杂的图形功能。但这样必须要由DSP来控制显示模块,而且其刷新频率受到一定限制。示波表的实时性要求非常高,所以对刷新率要求也就很高,并且液晶显示界面基本上只是显示框架和实时波形等简单的图形,所以我们就直接用FPGA产生LCD所需要的各种显示控制时序。

显示控制电路主要由两部分组成,一部分是LCD的时序控制电路,另一部分是显示数据的传输电路。下面我们就将围绕这两个方面做详细的介绍。