100MHz 数字存储示波表样机的研究与试制----数据采集系统设计

第三章数据采集系统设计

数据采集系统是数字存储示波表的核心部分,它完成由模拟信号到数字信号的转换,即模拟信号经调理通道后进入A/D转换成数字量,再将这些数字量存入缓存器FIFO,由DSP读回进行计算处理,最后送去显示。

3.1 A/D的选择

数字存储示波表要显示信号波形首先要对模拟信号进行采样。所谓采样就是对模拟信号进行量化的过程。而量化过程实际上存在着许多限制。首先,它要受到量化范围的限制。由于A/D总有一定的输入量程,超出了该量程,转换结果就会出现很大的误差。例如,信号如果超出了上限,那么A/D只能给出最大码值;反之,如果超出了下限,只能给出最小码值。这样,采样结果就会相对于模拟信号产生很大的畸变,不能有效的反映真实的信号信息。另外,A/D对量化值进行编码的位数决定了采样模拟信号的精确性。编码位数越多,对模拟信号的分辨率也就越高,采样出来的信号电压值也就更准确。在实际应用中我们选择的模拟/数字变换器(ADC)是ANALOG DEVICE公司的AD9288,它的基本性能描述如下:

◆两个八位模拟/数字变换通道,100MSPS采样率/每通道

◆低功耗:90mW/每通道(100MSPS时)

◆片内提供参考电压和采样、保持电路

◆模拟通道:475MHz模拟带宽信噪比:SNR=47dB@41MHz

◆模拟输入范围:1Vpp/每通道

◆单电压供电(+3.0V)

◆等待模式选择

◆两种数据输出格式

◆输出数据与拼接模式

AD9288是双通道八位单片模拟/数字转换器,具有内部的采样保持电路,是一款低价格、低功耗、体积小易于使用的优化产品。它工作在100MSPS转换率时同样具有出色的动态性能,并且两个通道可以完全独立工作。

这款模拟/数字变换器只需要单3.0V电源供电(2.7V-3.6V),提供编码时钟输入方式,在大多数应用领域,不需要外接参考电压或者是驱动器件。数字输出和TTL/CMOS兼容,并且有独立的输出供电引脚,支持多数字逻辑电压(2.5V或3.3V)接口。编码输入是与TTL/CMOS兼容的,并且8位数字输出能在2.5V到3.3V电压范围内工作(典型值为3.0V)。用户选择项提供联合等待模式、数据格式选择,数据拼接模式。在等待模式下,数据输出处于高阻状态。先进的CMOS工艺使得AD9288体积超小(7mm * 7mm * 1.4mm),采用48PIN_LQFP封装。

工业制品温度范围:(-40℃-+85℃)。

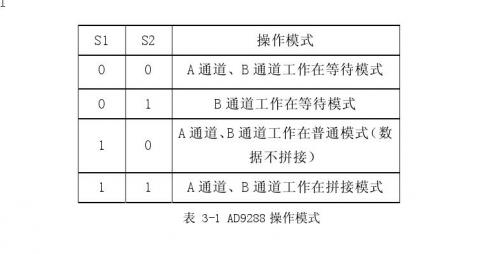

AD9288提供的S1、S2两个引脚可以用来选择多种操作模式。操作模式如表3-1.

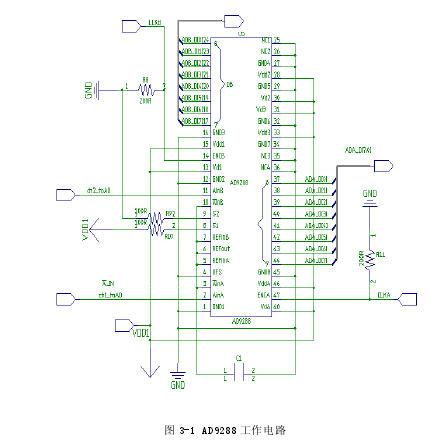

如表所示,当S1、S2都设置为1时,AD9288工作在双通道拼接模式。所谓拼接模式即是允许使用者将B通道输出数据错位半个周期。也就是说,向A、B两个通道提供相同的采样时钟(CLK_A=CLK_B),对同一信号进行采样。两通道的数据同在CLK_A上升沿有效。这样,在输出时B通道的数据就和A通道的数据相差180度相位。从而,使采样率达到了普通工作模式下的2倍。这一功能是非常有用的:如果用100MSPS的采样率对20MHz信号进行采样每个周期只能得到5个采样点,只能基本恢复和再现信号波形,如果利用相同的时钟,工作在拼接模式,将一个被测信号同时送入两个通道,就可以得到10个采样点,重现波形的效果会得到很大改善。我们在实际使用中,令其工作在普通模式下,两通道采集相互独立,及S1=1,S2=0.其具体连接图如图3-1所示。

3.2 FIFO的构成

当模拟信号被A/D采样进来以后,需要有一个能够快速保存采样数据的存储器。FIFO(First In First Out)是一种先进先出(即第一个读出来的数据就是第一个写进去的数据)存储器。它没有地址线,省去了寻址时间。另外,它还可以同时对存储空间进行读写。所以,它比一般存储器的读取速度要快很多。能够满足在高速采样时,对存储器快速读写的要求。在实际应用中,我们没有采用现成的FIFO芯片。而是利用FPGA里面自带的5K RAM,通过MAX-PLUS II调用它宏单元库MEGA_LPM里的库文件LPM_FIFO_DC,把它设置成为两个2.5K的FIFO.由于一个LPM_FIFO_DC库文件只能实现2n个存储空间。所以,我们调用了两个库文件(大小分别为2 9=512和2 11=2048)串连,来实现2.5K的空间。

具体连接如图3-2.

如图所示,一个LPM_FIFO_DC库文件有一个写使能信号wrreq,一个写时钟信号wrclock,一个读使能信号rdreq,一个读时钟信号rdclock,一个清除端aclr,8位数据输入线和8位数据输出线;同时还有两个状态端:FIFO满信号wrfull和FIFO空信号rdempty.它的具体工作原理是:1.写FIFO时,数据首先进入0.5K的FIFO.此时,0.5K FIFO读写使能同时有效,数据进入0.5K FIFO后,随即被写入到2K的FIFO.当2K的FIFO写满后,此FIFO模块的满信号有效,使得