100MHz 数字存储示波表样机的研究与试制----DSP 芯片的连接与配置(二)

时间:01-30

来源:3721RD

点击:

5.1显示时序控制电路

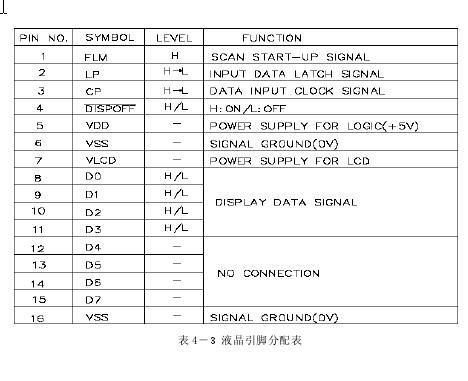

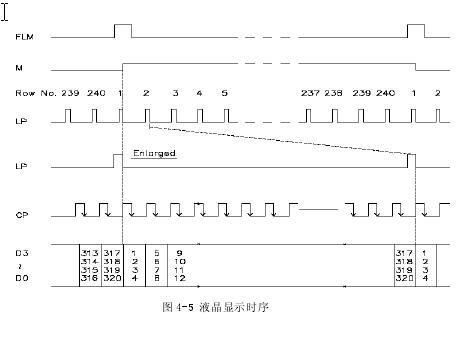

此液晶共有16根对外引脚,其引脚分配表见表4-3,其中有三根信号线,一根控制线,八根数据线。移位脉冲信号CP是指当来一个CP脉冲时,LCD读取数据线上的数据拿去显示。LP信号为行同步信号,即当CP读取完一行的数据后,产生一个LP信号,将数据锁存起来。FLM信号为场同步信号,即每显示完一屏数据产生一个FLM同步信号。D0~D7是显示数据传输信号线,其中D4~D7数据线无效,也就是说一个CP只进D0~D3四位数。DISPOFF控制信号是控制液晶是否显示的,当为1时显示,为0时不显示。

我们所使用的是320×240点阵黑白液晶,每个象素点只由一位数据表示。LCD显示从第一行开始,每产生一个CP,读取4位数据,这样要显示一行需要320/4=80个CP时钟,而液晶是240行,所以LP的频率是CP的1/80,FLM的频率是LP的1/240.其各时钟信号的时序图如图4-5所示。FLM的频率一般要求在175Hz~185Hz之间,所以我们在设计时把CP的频率设置在3.1MHz左右。

显示数据在FPGA内传输和DSP内部处理时我们是按两位表示一个像素点来处理的,当要显示波形的时候,再将这两位数相或后拿去显示。这样做的好处是只要稍许改变显示数据的输出方式,而不需对硬件和软件做大的改动,该系统就同样可以适用于彩色液晶显示屏。