APU GDDR5联姻 统一寻址到来

昨天,我们披露了Kaveri APU将会搭配GDDR5作为统一系统显存/内存的消息,AMD苦心经营多年的融合之路终将走开,不过无图无真相。看:

上图来自一份名为"Preliminary BIOS and Kernel Developer's Guide for AMD Family 15h Models 30h-3fh Processors"的AMD内部文档,目前仅提供给感兴趣的开发人员,用于初步研究新平台的BIOS和内核。

Family 15h指代的是整个推土机架构家族,Models 30h-3fh又是什么呢?在此之前,Models 00h-0fh指代的是初代推土机,Models 20h-2fh对应的是改进版打桩机(Piledirver)。Models 30h-3fh自然就是可以视作推土机3.0版本的压路机(Steamroller),Kaveri APU中整合的CPU架构就是它。再往后还会有Models 40h-4fh,也就是终极形态的挖掘机(Excavator)。

图中勾勒的这颗处理器拥有2-3个计算单元(也就是所谓的模块),对应4-6个CPU核心,不过奇怪的是AMD路线图上一直说Kaveri APU最多才四个CPU核心,或许这张图直接涵盖了更遥远的产品?

最有趣的地方出现在北桥,延伸出去了四个GDDR5控制器,但没有标注DDR3,而根据确切情报,Kaveri APU会继续支持DDR3、DDR3L。说不定经过一番过渡之后再下代就只用GDDR5了。

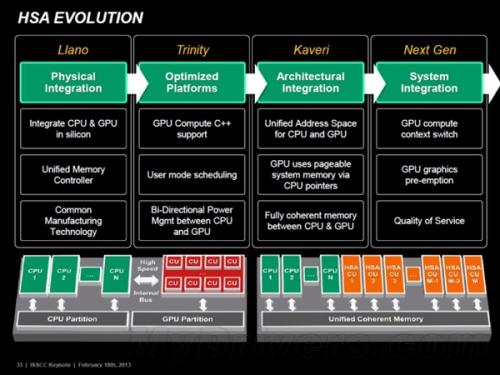

下边这张HSA异构计算架构同样可以说明问题:

经过Llano、Trinity的铺垫,Kaveri将会实现架构整合,在指令集架构(ISA)的层面上完成CPU、GPU完全一致性内存,支持统一寻址,GPU可以通过CPU指针使用可分页系统内存。

GPU与CRQ(一致性请求队列)之间的内部通道被称为"Onion"(洋葱),每个方向都拓宽至256-bit,可以满足HSA架构的需要,更快地在CPU、GPU之间交换数据。

再往后,还会有最后一步系统整合,那才标志着AMD融合大业的真正搞定。

这份文档中还提到了一条"Add PCIe endpoint mode"(增加支持PCI-E端点模式),猜测可籍此将Kaveri APU作为PCI-E设备接入其它系统,当个协处理器什么的。

AMD GDDR5 CPU Kaveri APU 相关文章:

- 彻底看穿双核CPU Intel与AMD多核处理器剖解 (07-12)

- AMD冲刺出货量 扩大晶圆代工厂下单(05-01)

- 多内核处理器应用趋势下的高性能视频系统设计(02-03)

- AMD将推处理器方案,力抢嵌入式大饼(01-18)

- APU与GPU共进 AMD抢攻嵌入式应用(02-13)

- AMD内部资料:如何通过创新架构和电源技术提升处理器能效(07-12)