高亮模式设置问题

时间:10-02

整理:3721RD

点击:

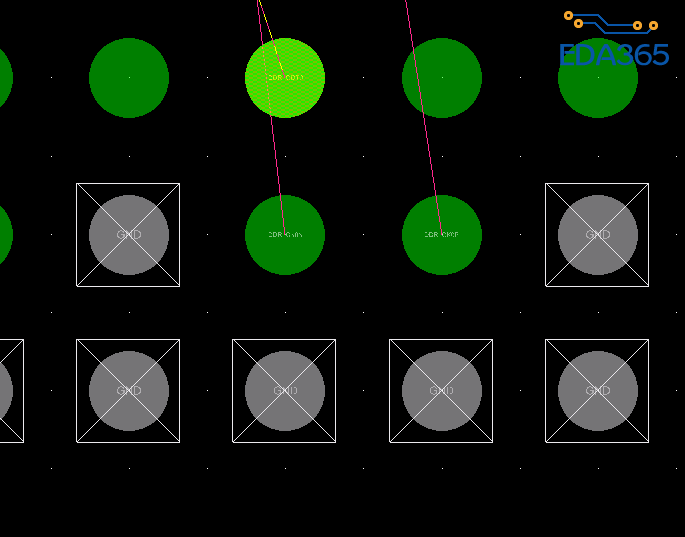

file:///C:\Users\lee\AppData\Roaming\Tencent\Users\1661454909\QQ\WinTemp\RichOle\2G@4@Y{A5QQTMPC9}L1BK1L.png如图所示:GND网络都有个正方形把它表示出来了,请问用什么方法设置的?

地网络加了一个Ratnests_Schedule属性就好了

Edit--->properties ,点选GND网络,在弹出窗口左侧找到并选中Ratsnest_Schedule,再到窗口右侧Ratsnest_Schedule栏赋予网络属性POWER_AND_GROUND搞定。

Edit--Properties--valtage

貌似你都会设置BGA格点了,却不会给GND设置POWER_AND_GROUND属性?

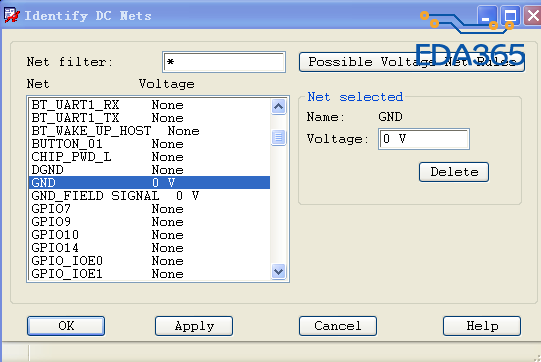

logic\identify dc nets

选中gnd,voltage填入0

楼上说的都对~~

楼上的楼上说的对

謝謝學習

学习学习

请问,BGA格点怎设定?

格点间距设置为BGA PIN间距的1/2 , 然后再把偏移量设为BGA任意一个PIN脚坐标就可以了。

感谢回复

只是,对于这种设定充满疑惑

如果将偏移量改成BGA的PIN脚坐标,这样板子的其它组件坐标就乱掉了

为什么要为了一颗BGA把整块板子的坐标弄乱呢?

这样设置的目的是为了方便摆放BGA封装的滤波电容,当然在BGA内打孔也方便很多,滤波电容布局完成后一般都会将格点还原,不存在其他组件坐标乱掉的问题。

另外,

如果仅仅是不想设置偏移量的话,

你也可以只单独移动BGA,

将BGA中心点与设置后的格点重合就行了。