PCB里面的规则删除,

你是否可以把板子导入到一个没有设规则的空板子上去,或者你导入一个规则替换原来的规则

原理图里面的网络确实很难删除干净,我也常常遇到这个问题,又懒得去原理图里面找规则,每次导完网标后都把PCB规则重新设置一下。设置好一次以后可以备份一下,就不用更新网标的时候每次都设置一次。这个也只是治标不治本,还期待大神来教教解决方法。

这样网标一更新又回到解放前了

我也想过你的方法,但是板子有3000个元器件,而且我已经模块复用了一部分,布局也已经差不多了,这样的话工作量太大了

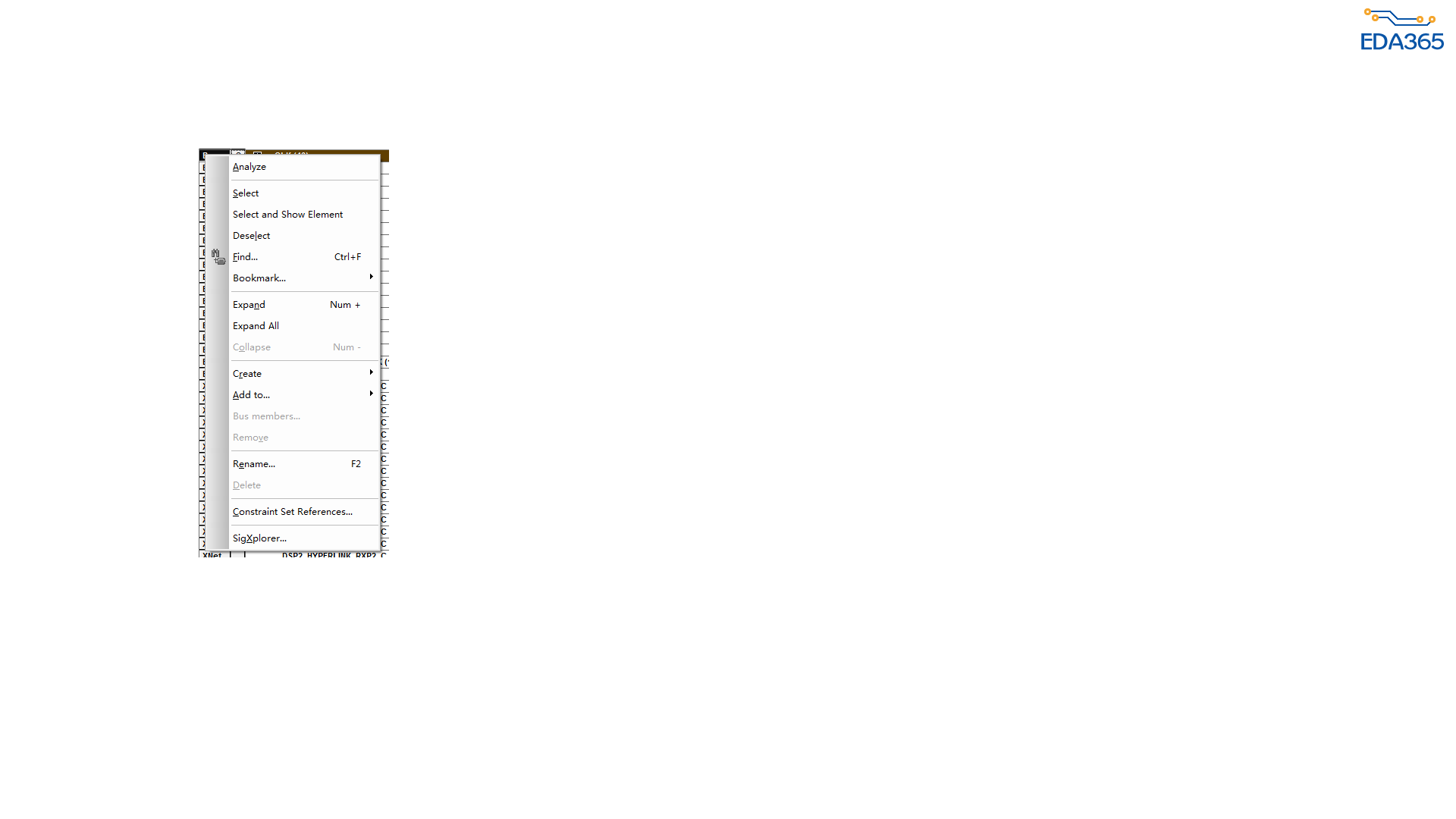

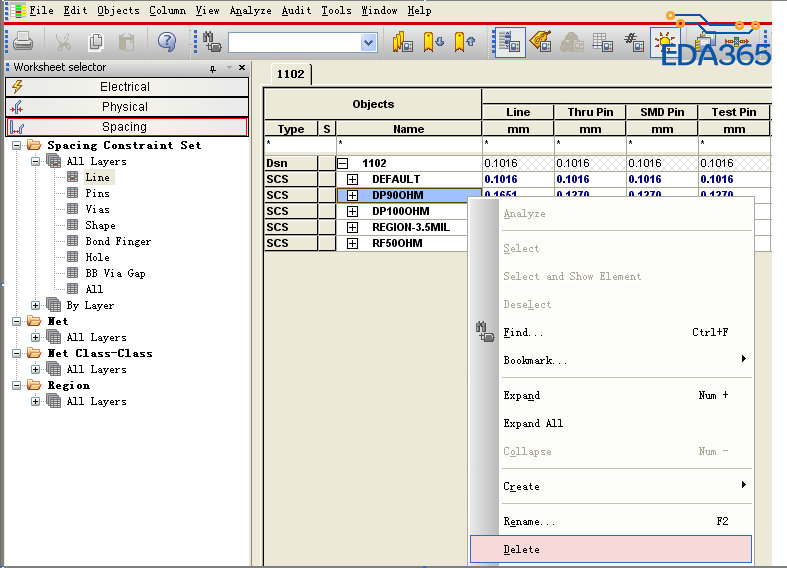

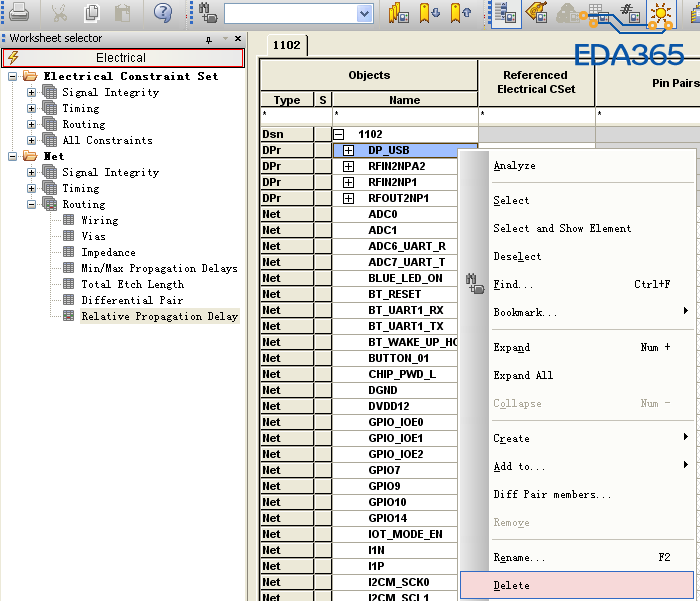

所有规则都是可以在约束管理器中删除的

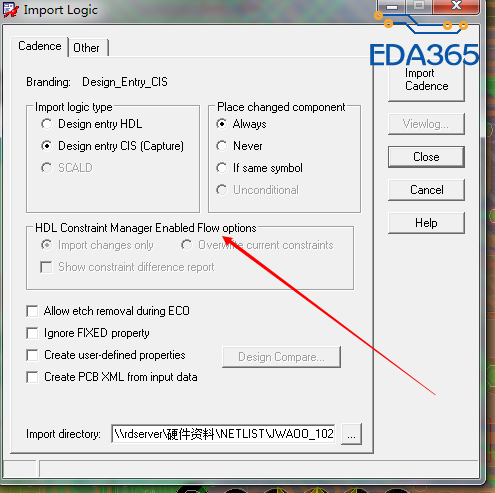

如果有在orcad在设置了规则,在allegro导入网表的时候,不勾选create user-defined properties,是不会导入在orcad中设置的规则

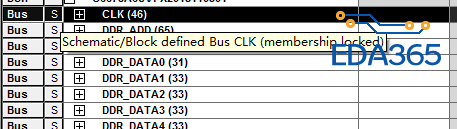

我的第二截图已经说明了,右击出现的选项,delete是灰色的,无法执行。另外你说的不勾选create user-defined properties,我现在就是这样的

1,删除PCB里面的BUS(看你图中是BUS),需要edit-property ,然后find里面选net,然后选中所有net,弹出的属性界面里面删除所有BUS即可;

2,删除原理图里面的约束,一般基于旧图修改完成后进行,切换到首页,选中dsn,然后右键选择edit object property,弹出界面中选择你想删除约束的类型,比如net,然后把BUS类型约束删了即可,如果有其他的,同样删了即可。一般来说约束一般针对这里的parts和Schematic nets以及flast nets,还有比较少的是pin,这几页框选删除即可,不用怕,不能删的不会删,从PCB倒进来的全没了,很简单,然后再导网标就不会把这些约束传递到PCB了。

可以直接删除BUS的吧

Tools->Database Check里面有个Purge unused constraints 就可以删除不用的规则了。

导网表的时候有个overwrite规则的选项

原理图里面的规则是删除了,但是没有用,导到PCB里面没有变化

没有变化

你说的在哪里?

不好意思,没注意是HDL格式的网表才可以选择