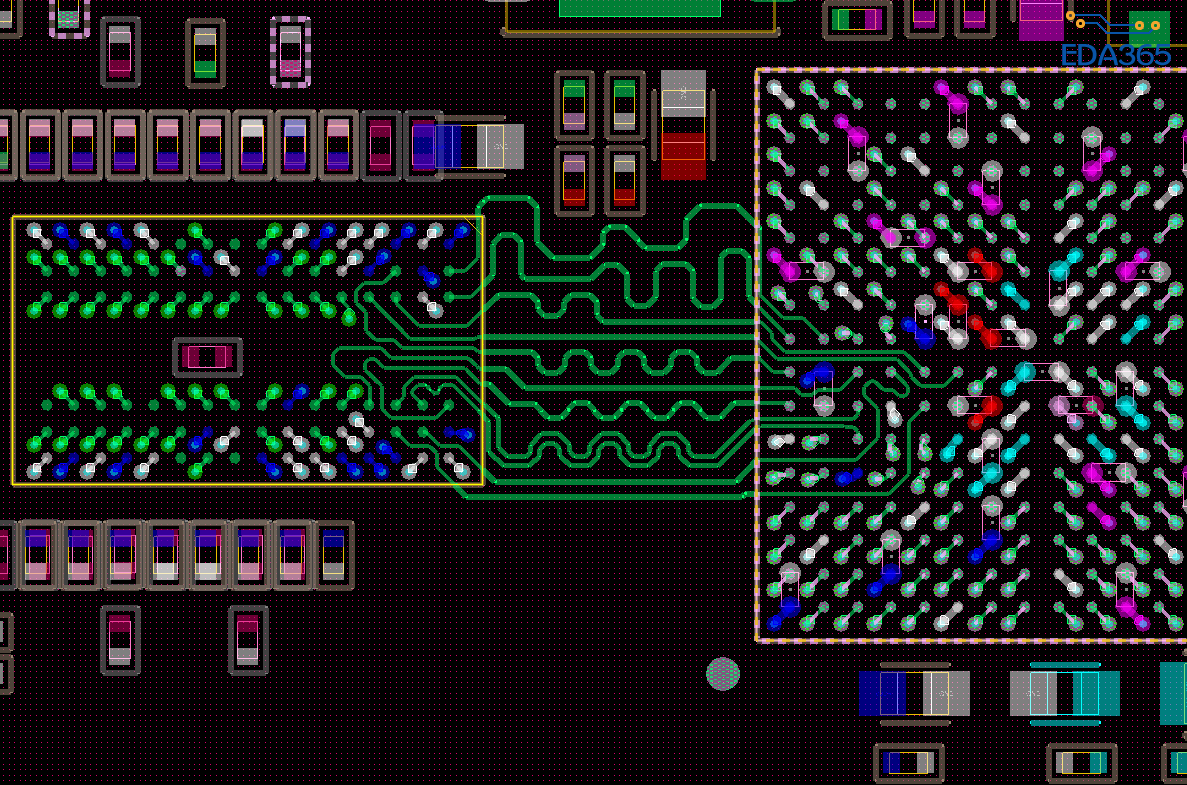

我绕的一组DDR3数据线等长,请大家拍砖!

时间:10-02

整理:3721RD

点击:

最短的735.4mil, 最长的749.15mil, 请大家看看有什么不妥帖的地方!

1 最上面两个dq线进芯片不用变细

2 差分线相位补偿应该靠近不等长的部分,就是ddr那头,而且那个绕的间距也有点小

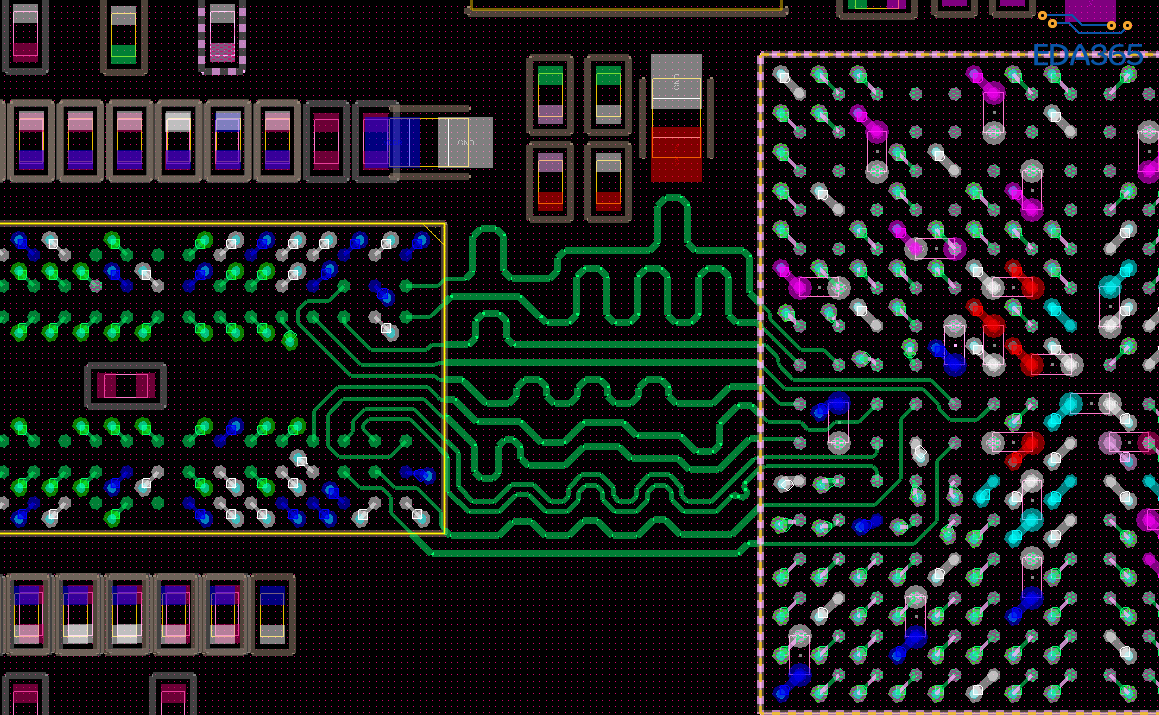

又重新绕了一下,请大家检查!

最好不要芯片底下绕等长,因为这段线细,越短越好

好的,马上改!

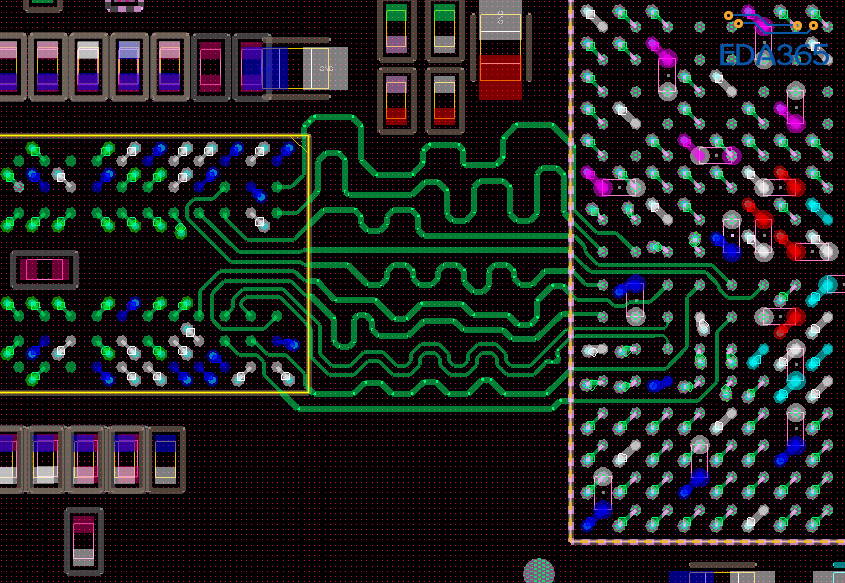

重新改过的等长,请麻烦再看看?

绕线的间距最好保持一致,那样会更美观一些,比如最上面那三根线绕得有点稀松了。可以再优化一下。

线宽尽量一致.变小的线宽越短越好.

学习一下:lol:lol

1.按照正常的叠层,表层到第二层的厚度在4mil,表底层走线在5mil左右,控制50欧阻抗应该不用变细

2.最外面一根不要绕,扩大走线区域,从而保证走线之间保证3w,尤其是dqs等其他差分

保证了质量的情况下美观也是收尾的好习惯

参考设计上要求40欧姆阻抗匹配,到第二层的厚度是3mil, 表层走了7.75mil.

不错,比之前的绕得漂亮。

你这是几层板啊,其他的地址线和数据线怎么办!

DQS上面那个绕的的dq线可以和下面的两个线换下线序,就不用绕了。