差分对为什么需要挖空处理?

时间:10-02

整理:3721RD

点击:

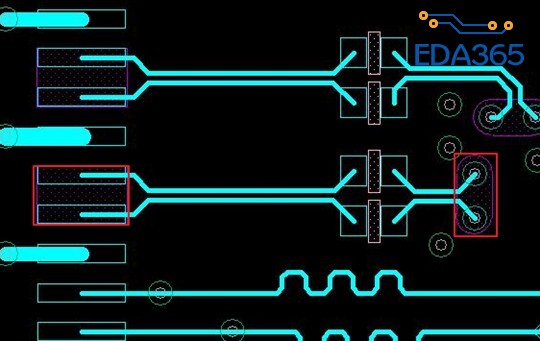

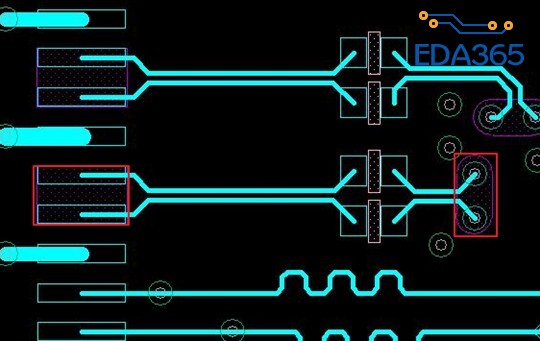

在差分对中,SATA via或者USB3.0 或者其他different pair,为什么在GND层和PWR层要挖空成(如下图红色区域,紫色图形为挖空形状)?

另外,放在top层的SMD零件,为什么要在pin的下方第二层也要做挖空处理?而在第三层补上GND?

另外,放在top层的SMD零件,为什么要在pin的下方第二层也要做挖空处理?而在第三层补上GND?

一个是抗干扰,一个是阻抗连续,至于具体就见仁见智了...

应该不是差分对挖空,而是差分对遇到比较大的焊盘的时候挖空吧,这个主要就是为了阻抗的连续性

都是为了是差分线的阻抗尽量连续

使用什么工具计算这个挖空区域的大小,才能保证这个阻抗是某一定值(譬如是50欧姆)呢?

在换层处就是阻抗变化处,为了不让阻抗突变而对信号造成大影响,一般在高速率信号设计中,会使用这种方式;普通板子无需这样做;

他这个是利用一个隔层参考的原理,所以你在对应的正下方挖掉就可以;

为什么要隔层参考?

这要看你的叠构和阻抗评估了,有时为了满足阻抗要求PP又太薄时就要挖空一层,参考另一层!

这个在连接器处挖空,是对差分阻抗连续性更好

高速板还有这样要求做差分!学习了 以前都没碰到过!

学习了

以前一直也没弄明白,学习了

不是挖空,是反焊盘,貌似为了保持阻抗的连续性

这说起来就讲究了,这是SI的活。