板中,如何局部设计某一根网络cline到shape 间的距离?

时间:10-02

整理:3721RD

点击:

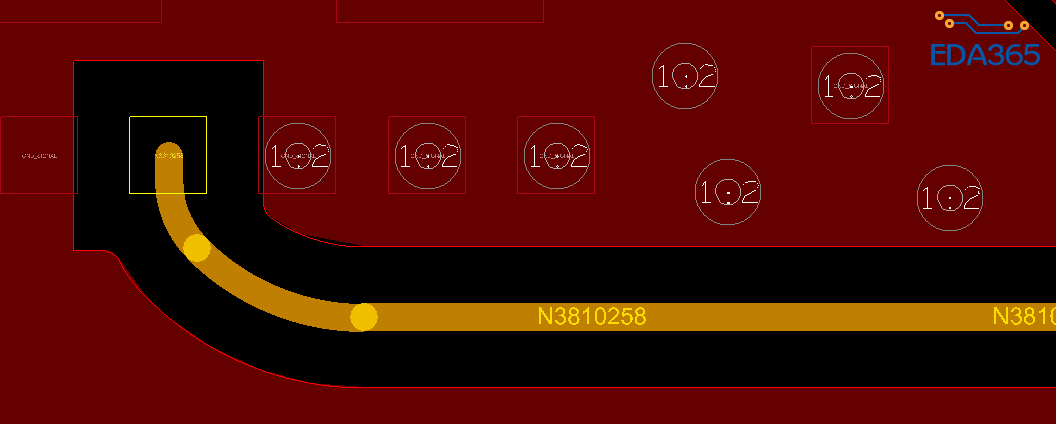

设计PCB时一般都是默认的安全间距5.98mil(line ---shape), 有时我们在设计天线时,需要加宽这一网络到周围shape之间的距离,因为是局部的操作,请教各位有啥好方法? 附图。

新建一个规则设置好间距,然后在这条网络上实施这个新规则就行了。

求详细步骤

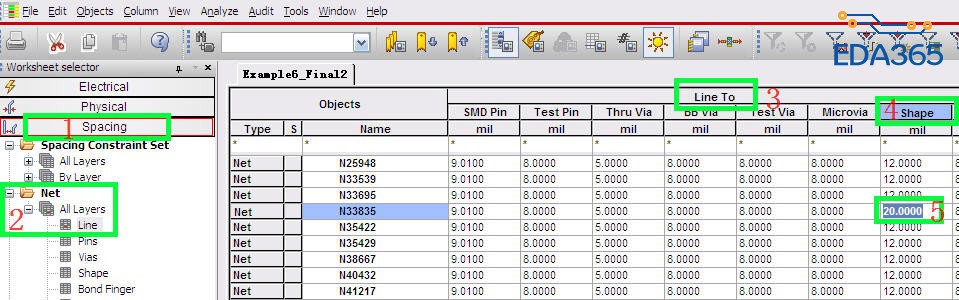

简单的做法就是到Constraint Manager中,在Sapcing的Net里面直接对网络设置Line to Shape的间距,如下图:

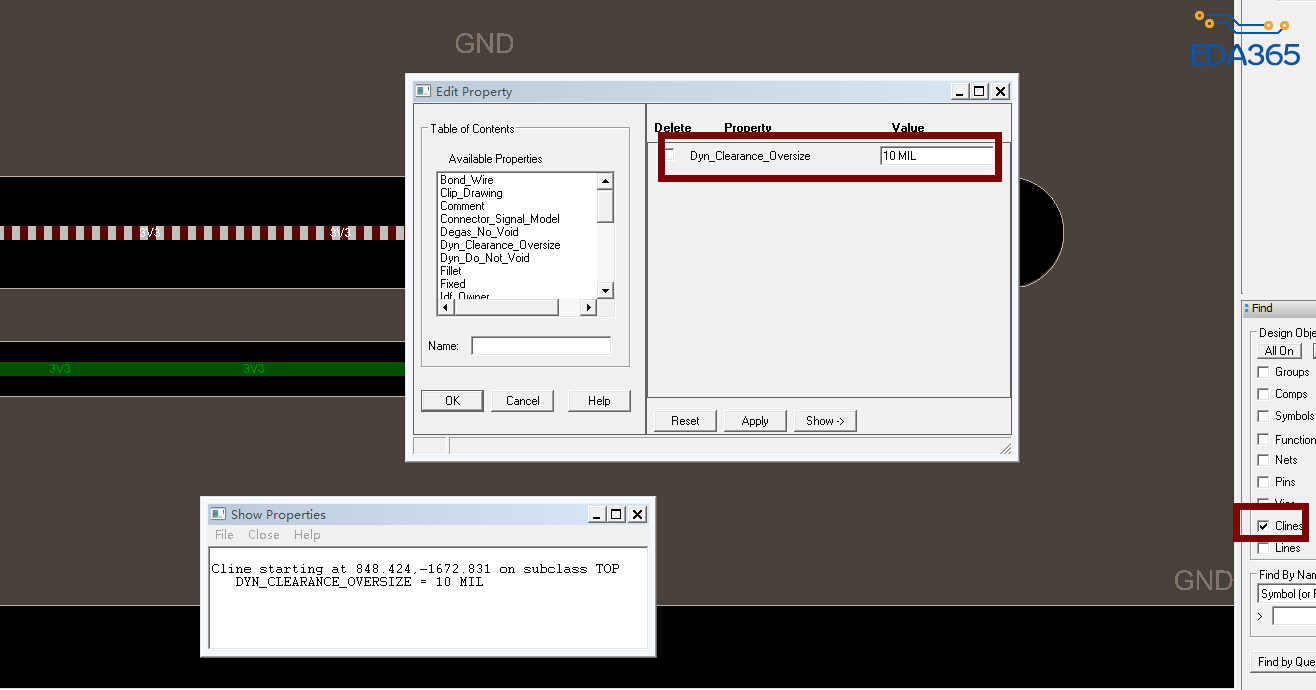

那如果这条射频线的相邻层也要挖掉相同宽度的铜皮,如何设置呢?

简单办法:打孔,先在相邻层走这个net的线,shape避让好之后,将shape改为静态的,然后删掉走线与过孔。

简单办法:打孔,先在相邻层走这个net的线,shape避让好之后,将shape改为静态的,然后删掉走线与过孔。

谢谢,知道了

:lol

楼上果然是绝招啊