vcc覆铜负片的时候为什么为出现这种错误,antiPad变小一点就可以了,大神们能解释下?

时间:10-02

整理:3721RD

点击:

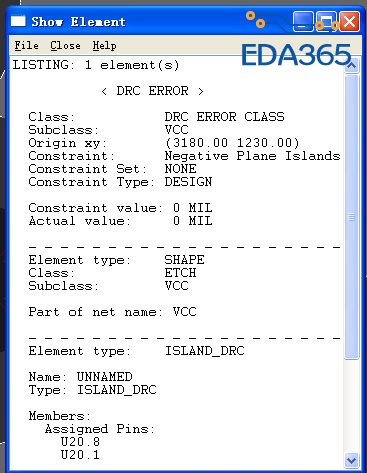

这是《cadence高速电路板设计与仿真 》上的一个例子,P271-273页,VCC被设置为negative,当对它进行动态覆铜的时候出现了D/I错误如下图一

大神们能说说这是什么原因?谢谢!我是菜鸟

大神们能说说这是什么原因?谢谢!我是菜鸟

图一

这是show element ,大概知道是与负片相关的问题,但是不知道具体的问题

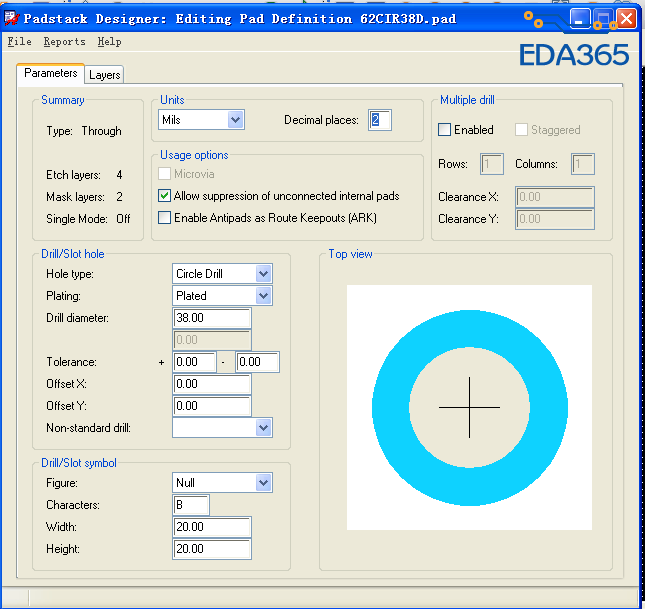

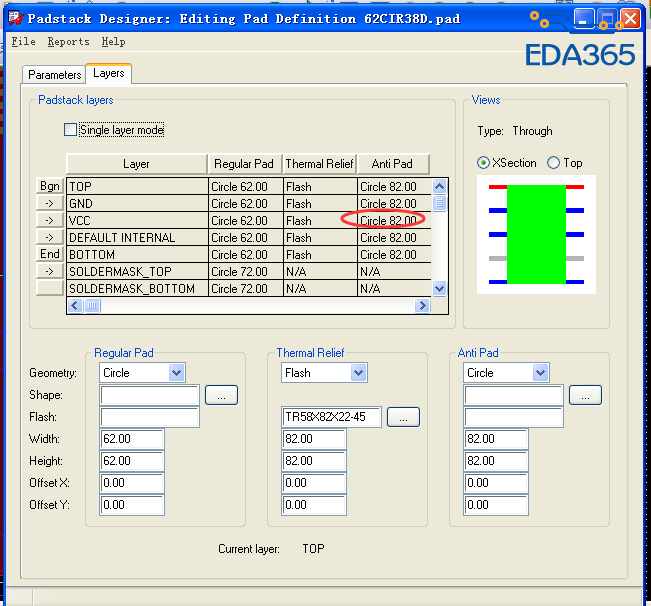

这是这个通孔焊盘的pad设置,书上说把vcc中的antiPad改为76就行了,或者在错误的地方挖个孔就行了

建议不要使用负片了,所见非所得,太容易出错了,如今电脑的配置完全能胜任正片数据

大神能看出来这是什么问题?

islands意味着按照孔的antiPad和周围的一圈避让会形成孤铜。

你把文件放上来看看

就是被anti隔离成孤铜了,你看你的anti,肯定是连在一起形成一个环了