这个DRC错误 是什么原因

时间:10-02

整理:3721RD

点击:

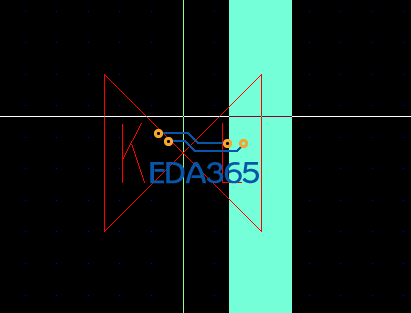

在设置 容许布线区域时候 产生了这个错误 如图

具体描述如下

LISTING: 1 element(s) Class: DRC ERROR CLASS

Subclass: TOP

Origin xy: (0.0000 27.4955)

Constraint: Line to Route Keepin Spacing

Constraint Set: DEFAULT

Constraint Type: NET SPACING CONSTRAINTS

< DRC ERROR >

Constraint value: 0 MM

Actual value: 1.143 MM

- - - - - - - - - - - - - - - - - - - -

Element type: SHAPE

Class: ROUTE KEEPIN

Subclass: ALL

- - - - - - - - - - - - - - - - - - - -

Element type: VERTICAL LINE SEGMENT

Class: ETCH

Subclass: TOP

part of an etch line

segment:xy (0.0000 0.0000) xy (0.0000 55.0000) width (0.0000) font (Solid)

- - - - - - - - - - - - - - - - - - - -

具体描述如下

LISTING: 1 element(s) Class: DRC ERROR CLASS

Subclass: TOP

Origin xy: (0.0000 27.4955)

Constraint: Line to Route Keepin Spacing

Constraint Set: DEFAULT

Constraint Type: NET SPACING CONSTRAINTS

< DRC ERROR >

Constraint value: 0 MM

Actual value: 1.143 MM

- - - - - - - - - - - - - - - - - - - -

Element type: SHAPE

Class: ROUTE KEEPIN

Subclass: ALL

- - - - - - - - - - - - - - - - - - - -

Element type: VERTICAL LINE SEGMENT

Class: ETCH

Subclass: TOP

part of an etch line

segment:xy (0.0000 0.0000) xy (0.0000 55.0000) width (0.0000) font (Solid)

- - - - - - - - - - - - - - - - - - - -

你板子中画了一个走线的禁止区域即routekeepin,表示线在这个区域走是合理的,如果出了这个区域线就会暴这个DRC,提醒你这根线走出了这个区域

没有出现?什么意思,还没有走线?那就做一遍DATABASE CHECK看看呗