导出网表的问题

时间:10-02

整理:3721RD

点击:

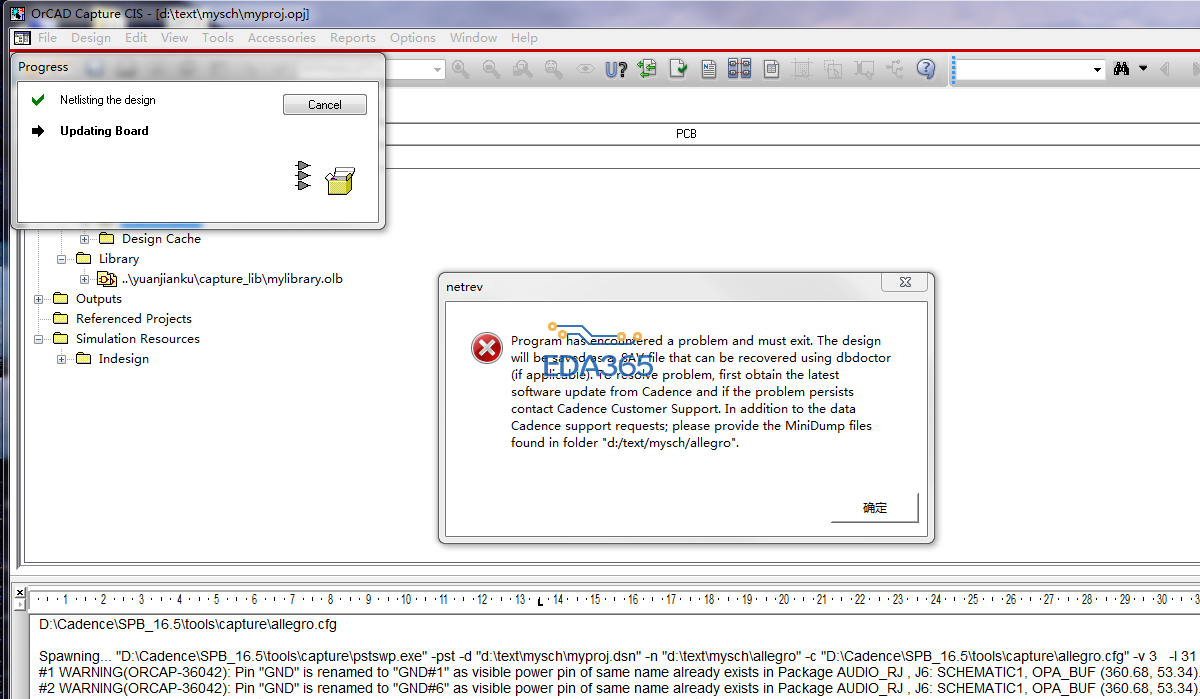

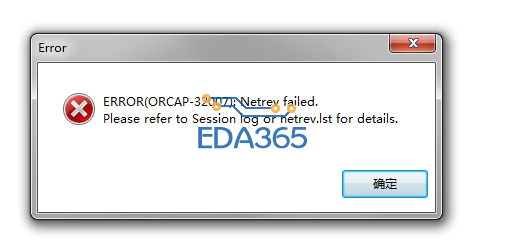

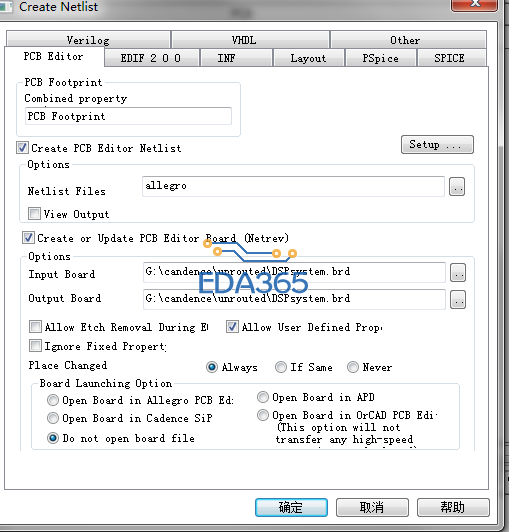

当导出网表示出现这种情况,请大侠指点一下!1,2附图是错误,3是我设置的!

你看下J6原理图中pin name有没有相同的,如果有,将它也不一样,导入的设定是正确的

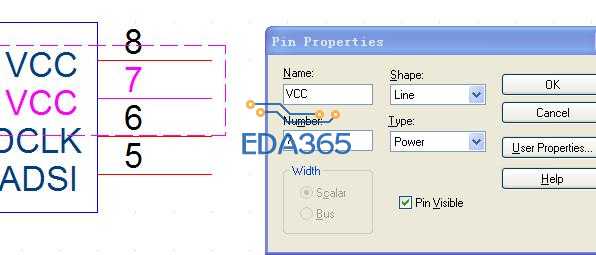

用allegro方式导网表对原理图要求比较高,管脚属性不能重复,例如不能出现两个管脚名为GND的管脚,可用GND1\GND2。区分

没有啊,怎么回事呢

那岂不是每一个GND都要编号吗

对的,即使是同一个器件内的gnd管脚都要区分开。你导网表时先看下drc有没有其他报错或者警告。

这里说的编号是器件管脚名编号,不是网络名。

小编的元器件封装是不是自己做的,当一个器件内有多个VCC 或者GND 做封装时 ,VCC和GND管脚TYPE 要设置成这样POWER,但是没有出错啊,LZ 你吧出错的 贴出来看看

你好,我是下的宇博士的资料,和他的视频 学习的 ,所以具体不知道怎么回事啊,还有你说的粘贴的资料,指的是什么

正常情况下封装中不能出现两个相同的名称。即vcc\vcc1等等,只有连接信号的时候可定义为一个信号名称。