BGA pin 间距只有0.5,线出不来,但是很多空脚,想从空脚上走线,如何设规则?

时间:10-02

整理:3721RD

点击:

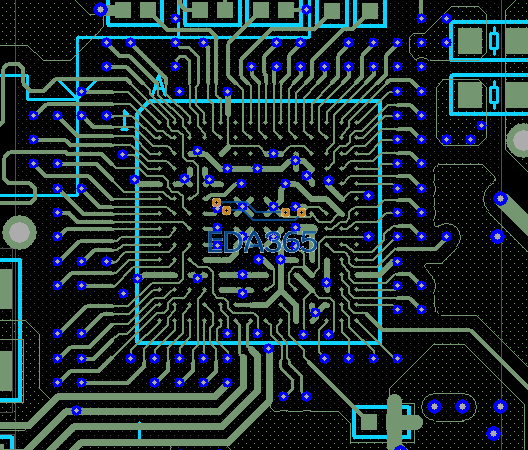

大家帮我看看,我有net 的pin想从没有net属性的pin上借道拉线出来,怎么设这样的规则?才能把线经过BGA没有net属性的pin走出来,如下面这样的图

设置SMD pin到line的距离,小到你能拉出线的程度,要不就扇出从其他层拉出来

0.5可以走线啊,看你要走多宽的线,一般3.1Mil是没问题的,但是你表层镀金厚度可能就只有0.5盎司了.

改symbol,把那些空pin删掉。

同意楼上说法

用HDI

如果是同一个BANK,相同电压,可以在原理图里设置swap pin啊,不过如果是CLK和RESET,和比较重要的信号就不行了,IO的可以。

另个办法,跟硬件工程师商量,能不能将没定义的NC脚定义为要出现网络。

前不久也做了一款0.5BGA的 最小线宽3.5mil;通孔设计,不知道你的0.5bga 有多深;贴个图供你参考。(此项目来自高清网络摄像机核心板)

阅读权限: 9

0.5 bga 通孔设计

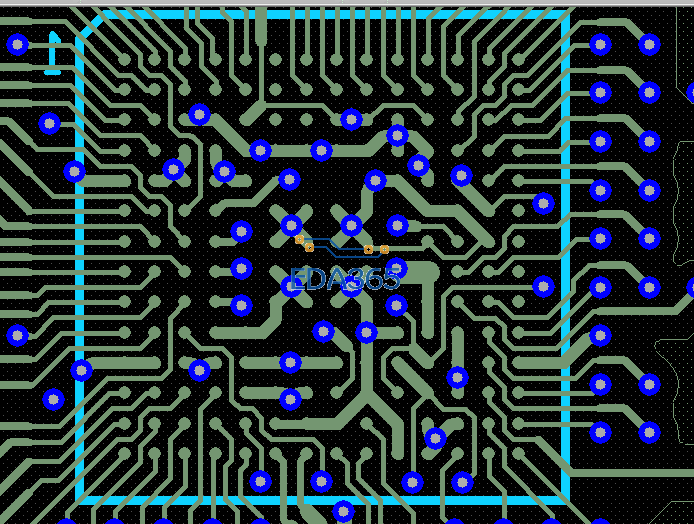

再贴一张大点的,

0.5 bga 通孔设计