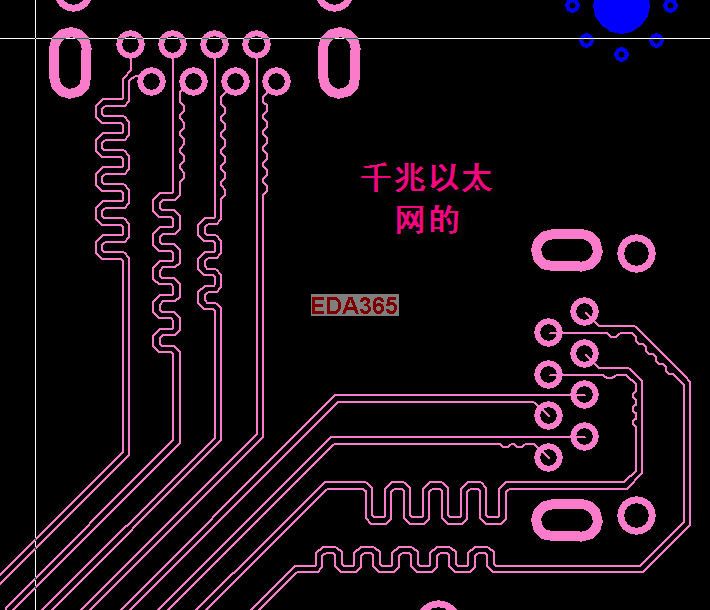

关于绕线控制

时间:10-02

整理:3721RD

点击:

差分对内绕线控制2根线误差在5mil之内,似乎很难啊,后放宽到50mil,还是有很多无法满足,难道要我放宽到100mil,如果放宽到100mil,不会有什么问题吧?我的信号线是100Mhz的时钟,从一个1进24出的时钟buffer出来的时钟走线保持等长。

你方法不对吧?5mil还算很好控制的!

应该很好控制的吧,难道是有什么特殊的绕线要求吗?

5mil的差分对等长是常见的差分规则设置,对于这种既有总长等长要求,又有差分对内的相位要求的,你先将差分对调到5mil以内的对内等长,再绕线调总长等长。

应该很好控制的,你是不是设置到2个组里了

我是先走完差分对,然后再绕线,但是绕线之前,发现差分对内2根线长度差异很大,不知道为什么?