请问这样的线怎样设置规则

第一次见到ddr走菊花的

可以试试用pinpair设置规则

很奇怪,不知道为什么是走菊花链,小编可以说下吗

设置好T点以后就可以进入CM中使用约束集对Pin Pair进行设置了

如果你所有做长度约束的网络拓扑结构一致的话只要设置一根就OK了

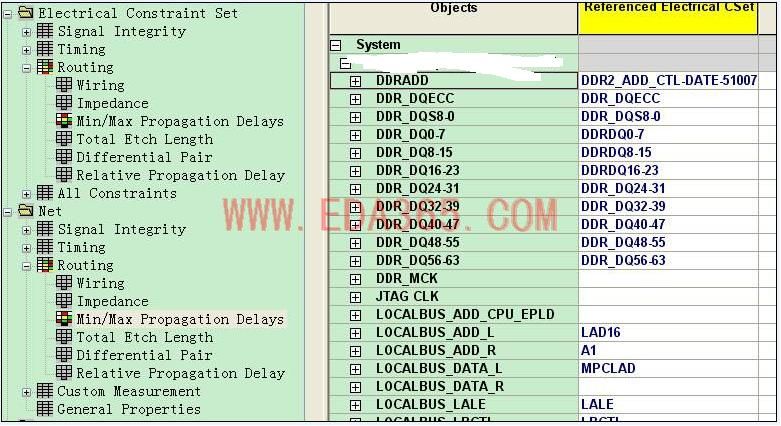

具体怎样设置,我在CM下 net/routing/propagationg delay中 有对DDR_A0, DDR_A1等分别设置pinpair, 接下来的不知道怎么设置了,应该不是一个一个数值的填吧,我所设置是这样的

http://www.eda365.com/viewthread ... ghlight=%2B58710780

刚看帖子,可是我的没仿真模块,有没有其它的办法

不用仿真模块,按上面的步骤来就可以了。

看看,研究一下

我的软件是没有装仿真这一块的,在装了仿真模块的机子上试了下,会出现下面的错误,好象行不通啊,能有什么方法解决,或者能否有别的方法在软件没装仿真模块的情况下设置

还有一点是我这个是有设置T点的,看了楼上介绍的帖子,好象T点并没设置进去

再顶一个,哪位大虾给看看,应该怎样设置规则

下面的是看前辈们的设置

且用楼上的方法打开sigXplorer后有下图

而我自己用楼上的方法设置

出现就是

哪位高手如有什么好方法,请帮忙抽点时间给指点下,谢谢了

没有T点可以加的

如果你能够进入SigXplorer

首先在其中编辑拓扑结构,按照你走线的要求,添加无损传输线就可以了

更新CM后会看到brd文件自动生成T点(前提是已经打开了网络鼠线)

完了以后你可以在SigXplorer中Set--Constraints操作设置其中的Prop Delay参数,根据你的要求都可以一次性设置完成

再次更新CM后,关闭SigXplorer,打开CM中的DRC显示

接下来就是见证奇迹的时刻,拉线吧...

上述是针对某一条Xnet做的长度约束

如果要做很多条Xnet,并且这些网络具有相同的拓扑结构的话

可以先做一个BUS,然后从这个BUS进入到SigXplorer中去

设置同上,然后生成一个约束集(就是总线的名称)

然后总线中所有的Xnet会自动生成T点

至此约束设置完成

谢谢楼上的热心解答,

首先在其中编辑拓扑结构,按照你走线的要求,添加无损传输线就可以了

请问是在哪个地方,我好象没找到,

我没有进行编辑拓扑结构这个环节,更新CM后,没看见生成T点

还有对于一组线,生成约束集,是在SigXplorer中Set--Constraints操作设置其中的Prop Delay参数之后么,还是有什么特别的地方

还有一点,我用其他的板子,因为没有用到模块,总出现下面的错误

如果能贴一些图看看,可能会更清楚,麻烦各位了

你的所有问题晚上9点网上帮你解决

请准时在线

好的,真是谢谢了