about how to do a RFIC + PA matching circuit design.

now i have a question about this project: TI do not supply the s parameater of this device. so i dont know the Zout of the PA pin,,, only we can get the Zopt Load.

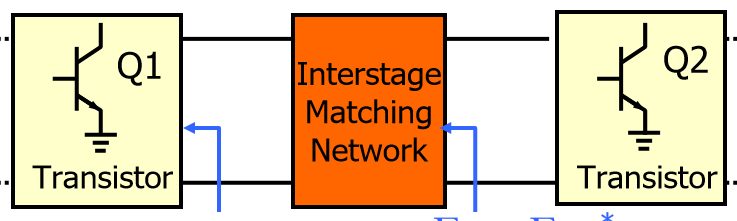

so how can i do the gain match between CC1120 PA pin VS LDMOS input ?

many thanks for your input .

Wh

They are closely related, isn't it?

not sure, but i just use the LDMOS demo sch, and match the input impedance of the LDMOS to RFIC Zopt load (and keep the same LDMOS Z load) (I know now the LDMOS Z load is not Z opt Load)... and i got η about 28% total. (RFIC + PA).

i have no idea how to tune the matching circuit.

...

hi cyberjok,

i think you have to use optimum load impedance given in the datasheet. just make sure you using bias condition for optimum load impedance for accuracy.

the other method is to do loadpull measurement for the device. Its require you to do TRL fixture for cc1120 for calibration and loadpull test setup. if you dont have it, you have to use datasheet impedance.

another way is to ask TI but i believe that they will give you the same value as in datasheet.

you mentioned that you getting 28% eff. how about power? are you getting good power? if yes, the optimum load impedance is for power and not efficiency. take note that optimum load impedance for power may not give good efficiency. a PA designer usually will choose impedance which give optimum power and efficiency. you can verify this with TI. good luck.

you mentioned that you getting 28% eff. how about power? are you getting good power? if yes, the optimum load impedance is for power and not efficiency. take note that optimum load impedance for power may not give good efficiency. a PA designer usually will choose impedance which give optimum power and efficiency. you can verify this with TI. good luck.

》》

Hello pragash, thanks for your input. 28% eff , RF Module (RFIC MAX RF POWER LEVEL + LDMOS OUT) 27dBm @ 6V 300mA; cc1120 will output +15dBm with opt load. and the LDMOS will give about 15dB gain<with Zopt load>. ... with the same bias condiction, I want make it output power up to 28.5dBm +;

>>>>

i think you have to use optimum load impedance given in the datasheet. just make sure you using bias condition for optimum load impedance for accuracy.

the other method is to do loadpull measurement for the device. Its require you to do TRL fixture for cc1120 for calibration and loadpull test setup. if you dont have it, you have to use datasheet impedance.

another way is to ask TI but i believe that they will give you the same value as in datasheet.

>>>

LDMOS input match to CC1120 Zopt load and then the LDMOS Zopt load will be change.... so if I tune the PA deivce Zout,,, PA input impedance will be change so CC1120 PA in Z load will be change...

I think between CC1120<-->LDMOS ,need to do gain match.

...

Using Zopt of the CC1120 allows it to deliver the maximum possible power to its load (whether it's an antenna or another PA). Using any other match will, by definition, result in the maximum output power of the CC1120 being lower. If you conjugate match, then the small signal power gain is higher, but you will get saturation at lower power levels.

So if you want maximum output power, use optimal power matching, not conjugate matching.

so you are just looking for addition 1.5dB more in your output power and satisfied with efficiency?

how do you did matching for the impedances?

what software do you use for simulation? do you have simulation model for cc1120 or just use the impedance from the datasheet?

I had try this way, LDMOS demo sch (the same bias condition) and change the input matching circuit to CC1120 Zopt load... but I just got about 26dBm,, tune the LDMOS Z load, max about 27dBm. as the datasheet it will be out over 29dBm.

btw the LDMOS is RQA0004PXDQS,DEMO SCH AS PAGE 6 SHOWS.

Hello ,I just use the ADS for getting the input impedance of the demo sch on page 6 (RQA0004PXDQS DATASHEET). and match to cc1120 opt load.

sorry about my poor English. thanks to all for your input.

hi cyberjok,

so you did conjugate matching in ADS using smith chart utility?

how did you simulate power/Harmonic balance without device model? if you just impedance from datasheet, you wont be able to get the power. how did you came up with 27dBm?