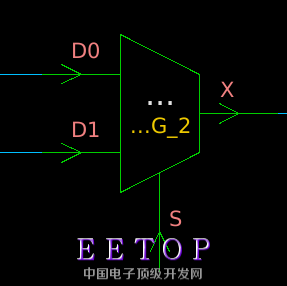

hold问题:launch和capture时钟经过同一个mux导致slack

时间:10-02

整理:3721RD

点击:

Startpoint:*

(rising edge-triggered flip-flop clocked by bclk)

Endpoint:*

(rising edge-triggered flip-flop clocked by aclk)

Path Group: aclk

Path Type: min

slack (VIOLATED)-0.1

slack是由于mux之前两个时钟的latency之差造成的,这种情况实际只有aclk --> aclk 和 bclk --> bclk 的hold检查,肯定不会出现跨时钟的情况,应该怎么约束?

方法一, set_clock_groups方法二, set_false_path

试着回答一下:在hold检查时capture路径选择最worst path,capture选择min path;

在ICC中 set timing_remove_clock_reconvergence_pessimism true

计算timing时,会把误差的那一部分补回来

如果回答的不对请各位大神指正 勿喷

不需要检查的path,与前端确认如果没问题 直接将aclk与bclk设置异步,或者针对这条path设false

学习了!

新入行小白试着回答一下,感觉这个问题是因为工具把两个无关路径做了时序分析,因此可以把aclk -> bclk的路径 set_false_path就行了吧