请教set_case_analysis的问题

是应该设在input上,还是应该设在source上,比如register的output

这里面有讲究吗?

还有个问题。一旦加载任何set_case_analysis文件后,pt就一条path都报不出来了。不设任何set_case,就不管对的错的,path都能报出来。

读了set_case后有以下warning..

Conflicted logic driving pin p3_pwr_mgt/p0_pwr_mgt_map/enclk_gkx_tclk_s_reg/Q, setting resolved logic value 0 on pin p3_pwr_mgt/p0_pwr_mgt_map/enclk_gkx_tclk_s_reg/Q. (PTE-042)

请问这是怎么回事?

我的理解是 你的Q 由于design的原因 和前面的constraint/input 造成Q的值和你set的值 conflict,

你这个reg是个static signal么? 不是的话 需要限制source,你往前trace一下 这个reg的input/source

设在input和output端上的结果是不一样的

请问小编,有什么区别?

设在哪里都是往后传播的,没有什么区别吧

这个应该可以猜出来啦

设在output端,对后面所有fanin都有效

设在input端,只对那个pin及后面有效

谢谢陈小编。还有个问题就是为什么我set_case了这个clk enable为0,可这个相应的clock还是在出来。该怎么block掉clk gating出来的clk?

这个要看那个clock gating的结构

谢谢小编。scan_mode已经在netlist里tie成0了。现在设的是这个enable为0,可gated_clk还有output.请问该怎么设?

谢谢。

set_case_analysis默认设定不穿过ICG

如果一定要做的话 case_analysis_propagate_through_icg true

谢谢小编,我已经设了。可是还是不行。还是有clock 跑进去。

另外,这个是我自己设计的clock gating,并不是dc产生的。

如果不是库里的ICG,而是自己搭的话,要用

case_analysis_sequential_propagation always

注意它的副作用:set_case_analysis 会超过所有FF一直传下去

这个我也已经有了。唉。很郁闷啊。

如果是自己搭的gate clock,直接在OR的输出端上set_case_analysis

多谢小编。已经可以work了。

原来后端有这么多的东西需要学习呀

请问一下set_case_analysis向前传播吗?

难道5,6楼讲得还不够清楚吗?

顶起~ 谢啦~

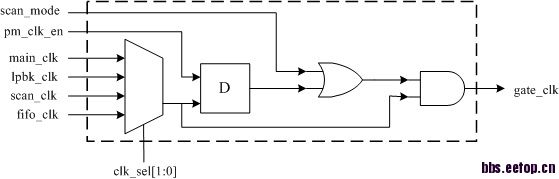

借用这个帖子,请教小编另一个相关问题,设计是这样子的:

在DC/PT中,我使用set_case_analysis设置了sel

但是在使用SOC Encounter中,分析这条路径还是出错,它采用了更坏的路径进行分析,感觉上跟没有设置set_casy_analysis一样

那么我的问题就是:在SOC Encounter这个工具里,我需要如何设置,才能得到正确的时序分析?

设在output端,对后面所有fanin都有效

设在input端,只对那个pin及后面有效?

这句话怎么理解?