set_case_analysis對sdf的影響

一個很簡單的MUX,設置了input_transition,為什麼註釋掉的部分寫和不寫

產生的a1.sdf不一樣?

pt里面写出来的吗?

是的,只是用了一個很簡單的NAND2,然後設了input_transition和load,不知道為什麼在set_case_analysis前write_sdf會對set後的write_sdf有什麼影響。

不好意思,理解不了你的意思。

小编你的意思是non.sdf和al.sdf不一样吗?还是指的什么?

因为不设case analysis时,PT扫所以可能的timing arc,报最差的一条,

如果设的话,PT就在设定的范围内找最差的

根据实际后仿真 对各种case进行设定来验证后仿的结果,不过不设的话,sdf应该更全面一些

不好意思,描述的不是很清楚,是这样的,我在做个实验,用一个很简单的NAND2,然后想看set_case_analysis对write_sdf

有什么影响,在实验过程中我一开始是分别将有set_case_analysis和没有set_case_analysis的pt脚本放在两个tcl是分别运行,假

设有set_case_analysis的那个脚本write_sdf得到的结果是a1.sdf,然后我嫌麻烦,就把两个脚本合起来,先在没有set_case_analysis

时write_sdf,得到non.sdf,然后在set_case_analysis后write_sdf得到a1'.sdf,按道理a1.sdf和a1'.sdf都是在set_case_analysis后

得到的sdf,不同的只是 一个是两个脚本单独跑,一个是合在一起,可是得到两个sdf的IOPATH的值确不一样,不知道为什么?谢谢~

了解!不好意思,描述的不是很清楚,是这样的,我在做个实验,用一个很简单的NAND2,想看set_case_analysis对write_sdf

有什么影响,在实验过程中我一开始是分别将有set_case_analysis和没有set_case_analysis的pt脚本放在两个tcl是分别运行,假

设有set_case_analysis的那个脚本write_sdf得到的结果是a1.sdf,然后我嫌麻烦,就把两个脚本合起来,先在没有set_case_analysis

时write_sdf,得到non.sdf,然后在set_case_analysis后write_sdf得到a1'.sdf,按道理a1.sdf和a1'.sdf都是在set_case_analysis后

得到的sdf,不同的只是 一个是两个脚本单独跑,一个是合在一起,可是a1.sdf和a1'.sdf两个sdf的IOPATH的值确不一样,不知道为什么?

谢谢~

两个sdf差多少?

合并的脚本中set_case_analysis的那条少了10%稍多一些

比较奇怪

查查PBA有关的设置(所有PT的变量设置)是否有true或者默认是true的,

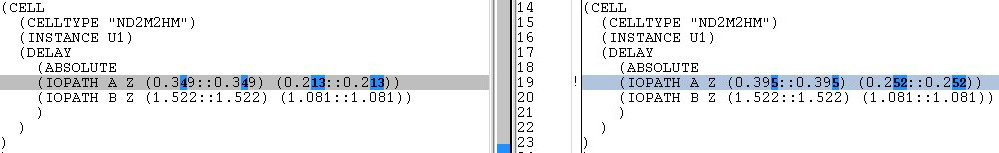

把那2条的delay贴上来

简单的NAND2,设了input_transition和input_delay,set_load,

然后write_sdf,左边的为合并后的a1'.sdf,右边的为单独跑的a1.sdf

版大,我顺便想问一下,对于XOR2,如果我set_case_analysis 0 B,那在sdf中

IOPATH (pos A)Z () ()

第一组数据是怎么算出来的,在B=0时pos A不能引起pos Z,所以不是很清楚怎么算的。

这个与你1楼的case analysis I pin没什么关系

你的netlist到底是什么样的,只是一个cell,还是多个cell在一个netlist里面,cell的pin都是各自独立的连接到port,还是共用某些port?

所以里面是空的

只有一个cell,就一个与非门,与非门的三个pin分别连到a b c三个port上,没有别的东西了,因为只是做个实验,无意发现两次的sdf不一样,1楼的MUX也是只有一个cell时,暂且不看,现在就说只有一个NAND2的情况。

那你的case analysis 设在哪个pin上?

是設在pin A上的,也就是出現不同值的那條path上的pin

哪个A->Z与non.sdf接近?

單獨跑的a1.sdf和non.sdf是一樣的。

可能是PT在计算设有case analysis的path delay时的特点(bug?)导致这样的结果

换个版本试试

我在set_case_analysis后加了update_timing -full,出来的结果就都是一样了,可是为什么只是update_timing,没有-full就不行呢?