关于dc综合和sdf反标问题

时间:10-02

整理:3721RD

点击:

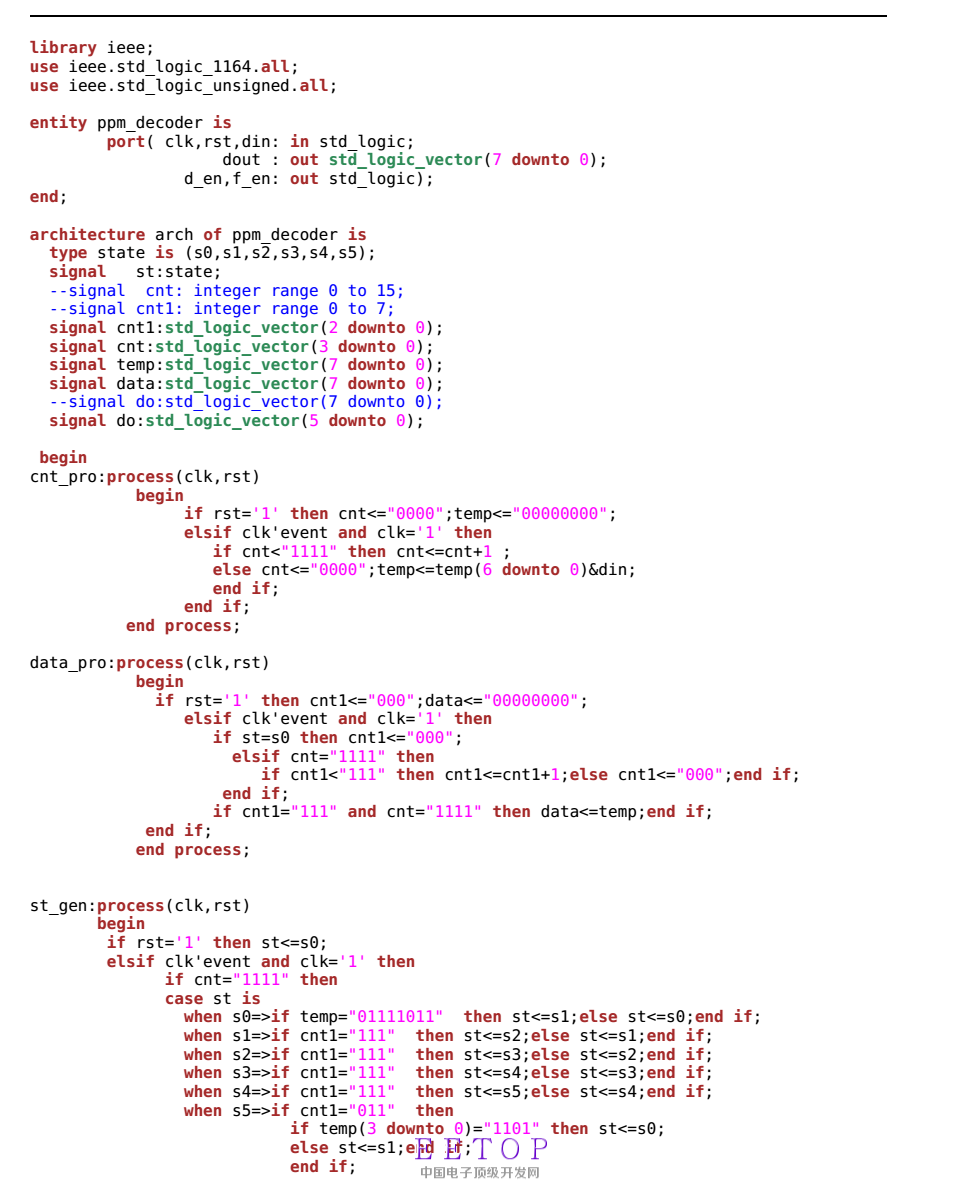

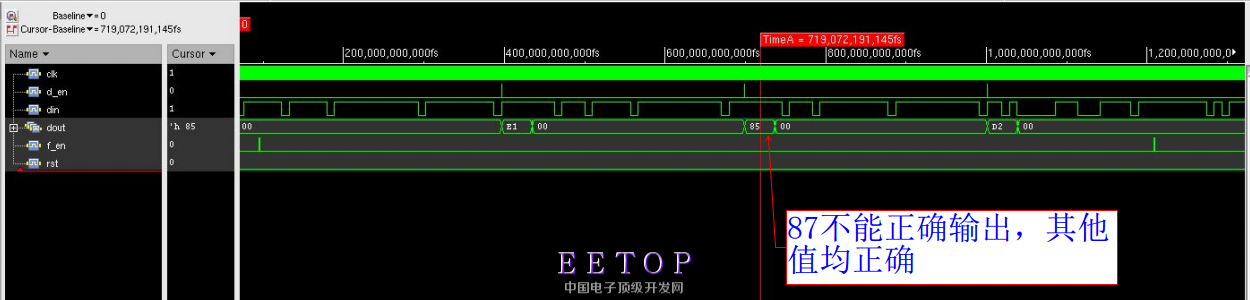

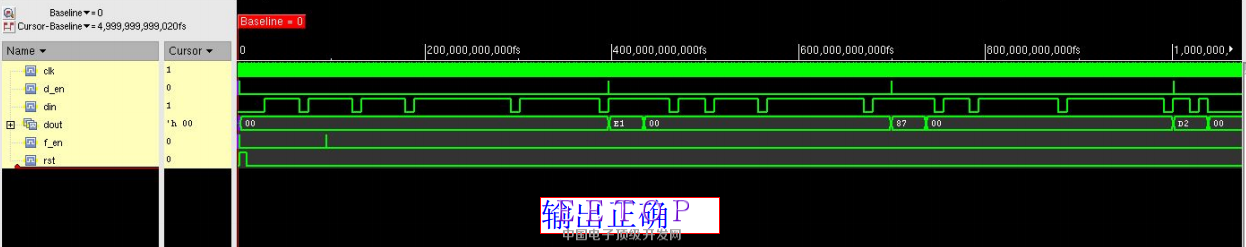

初学dc,写了个ppm解码的vhdl,功能级仿真正确,dc综合后再sdf反标仿真出现不定态和部分结果不能输出。但是dc三次后的sdf反标仿真结果正确。代码:

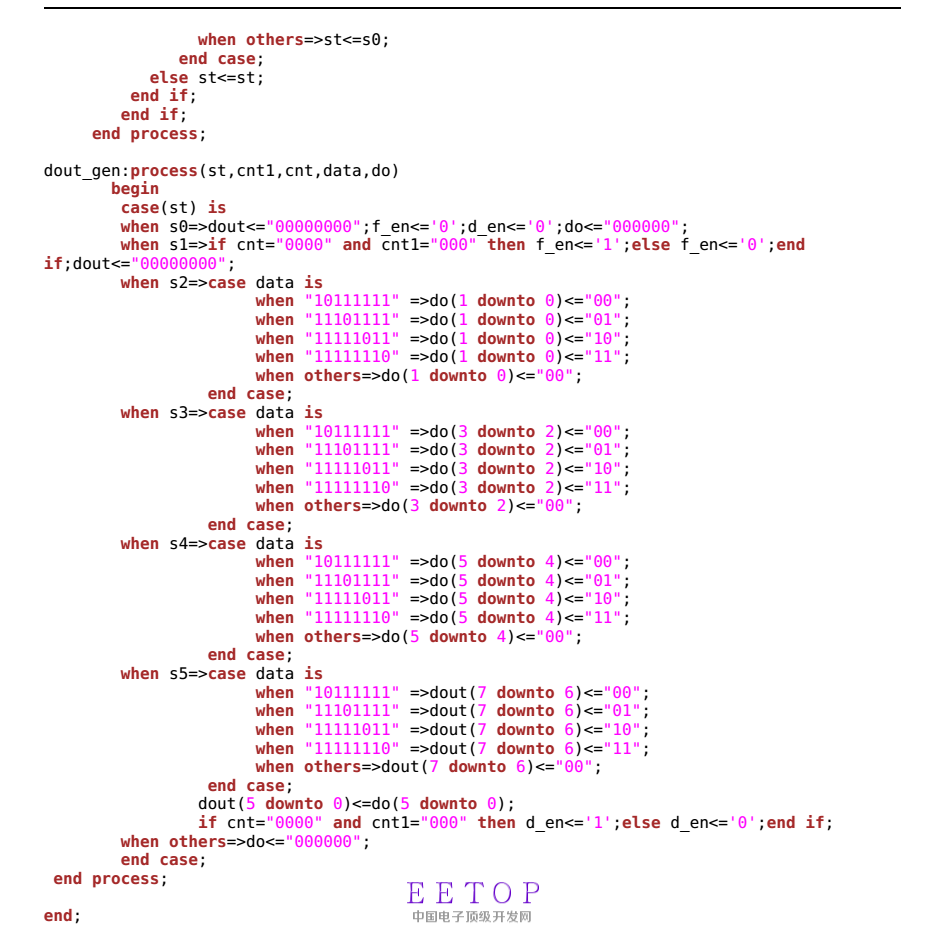

,dc的tcl文件

,dc的tcl文件 ,

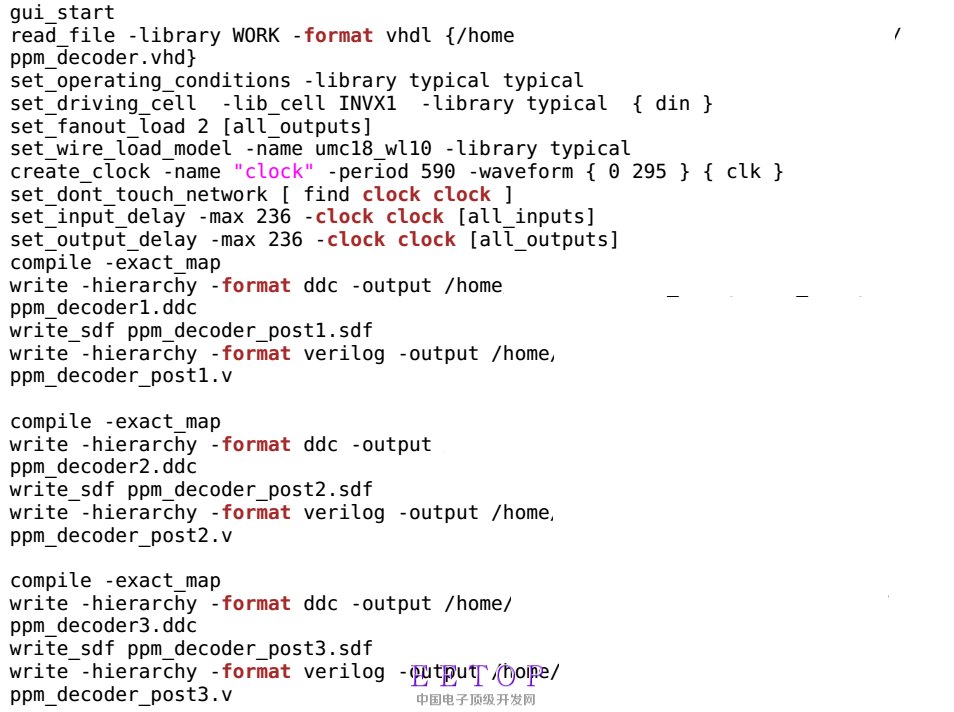

,共compile三次,分别保存三次.sdf和.v文件,三次sdf反标波形

这是为什么呢?vhd是否有问题?三次dc出来的电路是不同的,但是老师说不应该不同。这种问题是否合理

这是为什么呢?vhd是否有问题?三次dc出来的电路是不同的,但是老师说不应该不同。这种问题是否合理

1. 如果你没有用多线程方式跑的话,三次的结果应该是相同的,后面的会重新跑的,要优化的话用compile -incremental;

2. check_timing看你是否约束正确,或者有没有约束到的地方;

3.input/output delay太大了吧

4. 跑完之后你要分析时序是否已经满足了,我没看到你上面的约束文件里面有report_timing,时序都不满足的话你做什么后仿

谢谢!1. 请问什么事多线程DC?DC的话我只是使用了上面tcl跑了一遍

2.check_timing后有warning:there are input ports that only have partial input delay specified.------clk,rst,din

和the following end-points are not constrained for maximun delay...

3.时序是满足的,另外一个tcl文件里跑过所以这里没有加上。然后将input 和output delay 改为2ns 后,slack为585.29.

如果综合确实没问题的话,那么有可能是你testbench中复位信号的问题,不要和时钟边沿对其试试。

rst和din均设置在时钟下降沿变化的。

受教了

回复1# FreyaOu

感謝分享