为什么增加双孔会让timing变差

时间:10-02

整理:3721RD

点击:

为什么增加双孔会让timing变差?从原理上讲,应该是什么?

增加双孔不会让timing变差

先问是不是,再问对不对

个人觉得增加双孔理论上是为了timing变好,但是在你的设计资源减少的情况下屏蔽线时钟等可能会增加绕线了,出现加双孔让timing变差的判断。额

哈哈,我可能表述有误,其实我是想请教:如果影响到了timing,那么是引入了什么新因素,影响到了timing?

请教前辈,如果影响到了timing,可能是新引入的什么因素导致的呢?我想,增加双孔,绕线资源变得更紧张,因为要预留空间

目的是为了DFM吧,不是为了timing,个人理解

双孔会改变连线的RC,当然时序会有点变化

请教前辈,可以具体解释下吗?RC为什么变化?做了实验,没分析出什么

可能是。双孔会占据更多的布线资源,布线紧张的情况下,增加了绕线,改变了RC吧。

增加double VIA,除了DFM需求

Setup time 因為阻值變小會變好

Hold time 卻有可能因為data path上阻值變低

跳出新的violation. 不過violate 值通常不會太大

很高兴收到您的回复。有个疑问:

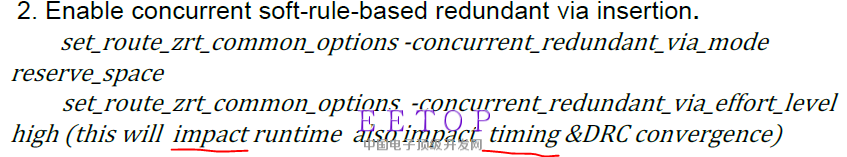

按照您说的会影响timing,在应该怎么设置slcak大于多少的才去做redu via?需要迭代试一试吗?还是一般有个经验值?一般在做case时,flow上应该怎么做?

之前看文档看到过,刚刚找了下没找到,大致意思是:

对于短线,双孔会增加电容(RC变大);

对于长线,双孔会减少电阻(RC变小)。