Scan中插入的lock_up latch原理是什么呢?

时间:10-02

整理:3721RD

点击:

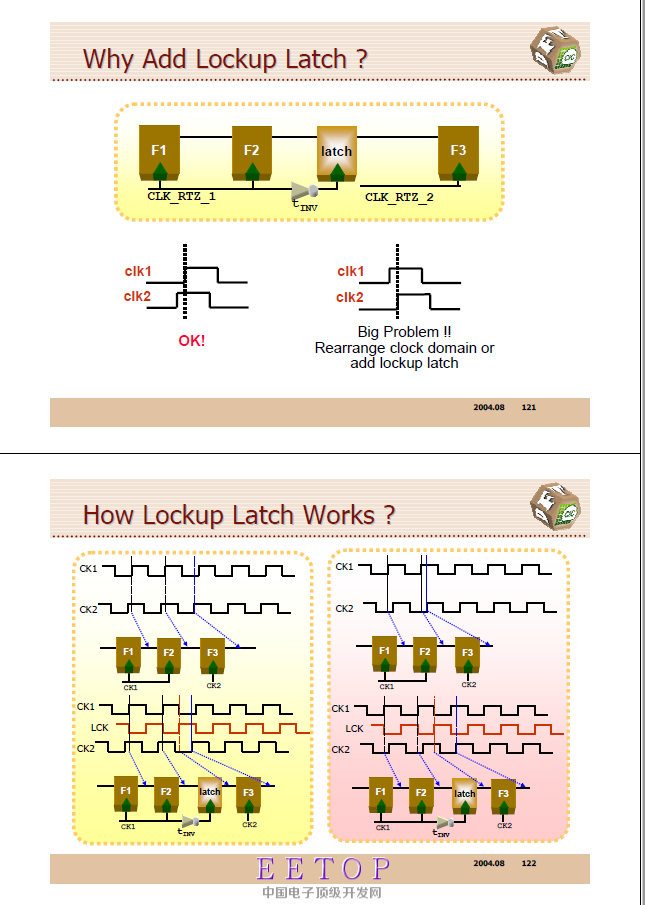

最近在学习DFTC设计scan chain,为了平衡scan chain需要设定mix clock,需要设置允许插入lock_up latch在不同的clock domain间。资料中写mix_clock可能会导致hold violation,而插入lock_up latch可以避免这一点。表示没有想明白。为什么会有violation以及插入lock_up可以避免violation的原因是什么呢?谢谢啦。

你好。后来这个你搞清楚了么?我也想知道

latch 的有效电平能保持半个周期

把clock锁半个周期,不至于数据太快,这样就很少出现hold问题了,一般实在跨clock domain的时候去插这个lockup latch

3楼正解吧。latch cell 的特点就是电平触发而非边沿触发,电平触发可以“timing borrow”,画一下波形图就知道了,可以借半个时钟周期,让hold check 多出半个时钟周期的margin。

其实这就是一个 hold timing check 问题。