多周期路径检查时为什么hold的设置比setup要少一个周期

多时钟周期或者多周期路径检查的时候,如果setup设置成N,那么hold需要设置成N-1;即是说

Thus, in most designs, a multicycle setup specified as N (cycles) should be accompanied by a multicycle hold constraint specified as N-1 (cycles).

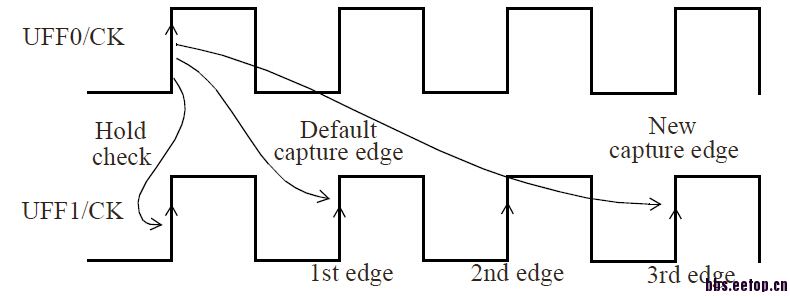

如下图

能否解释一下原因呢,难道hold检查的时候就用2nd edge不可以吗

上面示意图不就是如果3 edgechecksetup,2edge就check hold吗

但是实际要求的hold capature edge应该是第0个 而不是2nd edge;

我已经知道原因啦

就是第二个,

set_multicycle_path第一句Setup设置后是默认的Wave Pipelining,也就是延时变大、带宽不变的“真MultiCycle”,这个对OCV要求很严格,总体来说没什么人敢用......第二句Hold设置后变为带宽至少减半的“假MultiCycle”。

原因如下,两种说法,本质是一样的:

因为如果是默认的,即hold的capature edge is prior to setup capature edge,This imposes a restriction that data can only change in the one cycle before the setup capture edge as the figure shows. Thus the data path must have a min delay of at least two clock cycles tomeet this requirement. Here is such a path report.

说法二:hold 是对前后两个flipflop在相同时钟沿的检查.设了n-1就是返回n-1个周期做hold的检查,满足了两个flip flop在同一个时钟沿。如果没有-hold默认是检查n前一个有效时钟沿,如果n>=2,hold的检查就不是在同一个时钟效沿,对hold的要求就要多n-1个周期,那样太苛刻了,一般时序无法收敛。

能详细说一下吗?wave pipelining? 对OCV要求很严格,怎么体现?