vcs后仿遇到$hold问题

代码用modelsim反标sdf的方法仿真波形是对的,但是用vcs后仿的时候,遇到以下问题:

"csm18ic.v", 8026: Timing violation in testbench.bs_modify.comp_h_reg_reg

$hold( posedge CK:900000, posedge RN:900000, limit: 500 );

"csm18ic.v", 8026: Timing violation in testbench.bs_modify.comp_l_reg_reg

$hold( posedge CK:900000, posedge RN:900000, limit: 500 );

"csm18ic.v", 8026: Timing violation in testbench.bs_modify.count_reg_0_

$hold( posedge CK:900000, posedge RN:900000, limit: 500 );

"csm18ic.v", 8270: Timing violation in testbench.bs_modify.count_reg_1_

$hold( posedge CK:900000, posedge SN:900000, limit: 500 );

"csm18ic.v", 11567: Timing violation in testbench.bs_modify.sp_reg

$hold( posedge CK:900000, posedge SN:900000, limit: 500 );

"csm18ic.v", 11207: Timing violation in testbench.bs_modify.sn_reg

$hold( posedge CK:900000, posedge RN &&& (xSN == 1'b1):900000, limit: 500 );

"csm18ic.v", 7967: Timing violation in testbench.bs_modify.comp_reg_reg

$hold( posedge CK:900000, posedge RN:900000, limit: 500 );

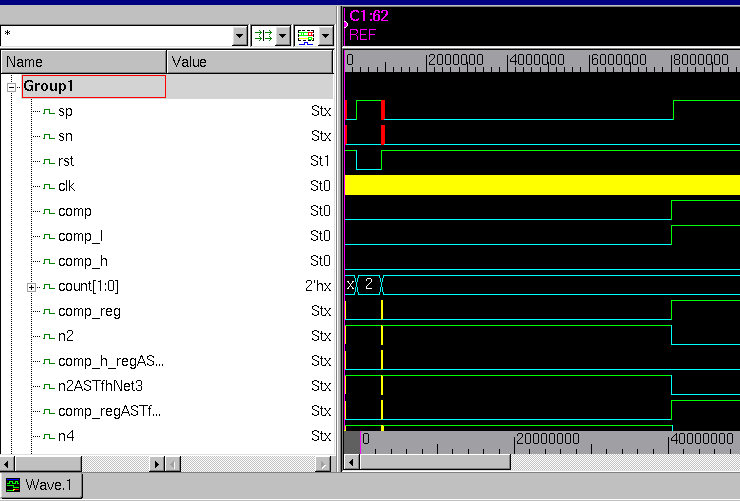

还有一些,问题跟上面的这两类一样,不明所以。求指教。上个仿真图:

之前听过一段话:后仿的时候sdf不能有hold违反吧。

同向各位大神求助这句话是否有问题

reset结束之前波形都是对的,但是在reset结束的时候sp、sn出现了x态,是vcs哪里没用对还是时序确实有问题,求指教。

好吧,之前的问题是因为sdf没标上。但是标上以后出现了下面的问题:

SDF Info: +pulse_r/100, +pulse_e/100 in effect

Warning-[SDFCOM_IWSBA] INTERCONNECT will still be annotated

DSM_201302.SDF, 377

module: XOR2XL, "instance: testbench.dsm_201302_inst.add_38.U2"

SDF Warning: INTERCONNECT from add_38.U2.Y to

add_0_root_add_0_root_add_41_2.U36.B0 has Instance at DSM_201302_HIER.v:393,

delay will still be annotated.

Warning-[SDFCOM_UHICD] Up-hierarchy Interconnect Delay ignored

DSM_201302.SDF, 902

module: DFFSRHQX1, "instance: testbench.dsm_201302_inst.P_reg_0_"

SDF Warning: INTERCONNECT Delay to up-hierarchy destination accOutput is

ignored, DEVICE Delay on port 'Q' applied.

Up-hierarchy interconnect delay arises when the load is hierarchically above

the source.

Warning-[SDFCOM_UHICD] Up-hierarchy Interconnect Delay ignored

DSM_201302.SDF, 903

module: DFFSRHQX1, "instance: testbench.dsm_201302_inst.P_reg_1_"

SDF Warning: INTERCONNECT Delay to up-hierarchy destination accOutput is

ignored, DEVICE Delay on port 'Q' applied.

Up-hierarchy interconnect delay arises when the load is hierarchically above

the source.

Warning-[SDFCOM_UHICD] Up-hierarchy Interconnect Delay ignored

DSM_201302.SDF, 904

module: DFFSRHQX1, "instance: testbench.dsm_201302_inst.P_reg_2_"

SDF Warning: INTERCONNECT Delay to up-hierarchy destination accOutput is

ignored, DEVICE Delay on port 'Q' applied.

Up-hierarchy interconnect delay arises when the load is hierarchically above

the source.

Warning-[SDFCOM_UHICD] Up-hierarchy Interconnect Delay ignored

DSM_201302.SDF, 905

module: DFFSRHQX1, "instance: testbench.dsm_201302_inst.P_reg_3_"

SDF Warning: INTERCONNECT Delay to up-hierarchy destination accOutput is

ignored, DEVICE Delay on port 'Q' applied.

Up-hierarchy interconnect delay arises when the load is hierarchically above

the source.

Warning-[SDFCOM_UHICD] Up-hierarchy Interconnect Delay ignored

DSM_201302.SDF, 906

module: DFFSRHQX1, "instance: testbench.dsm_201302_inst.P_reg_4_"

SDF Warning: INTERCONNECT Delay to up-hierarchy destination accOutput is

ignored, DEVICE Delay on port 'Q' applied.

Up-hierarchy interconnect delay arises when the load is hierarchically above

the source.

Warning-[SDFCOM_UHICD] Up-hierarchy Interconnect Delay ignored

DSM_201302.SDF, 907

module: DFFSRHQX1, "instance: testbench.dsm_201302_inst.P_reg_5_"

SDF Warning: INTERCONNECT Delay to up-hierarchy destination accOutput is

ignored, DEVICE Delay on port 'Q' applied.

Up-hierarchy interconnect delay arises when the load is hierarchically above

the source.

Warning-[SDFCOM_CFTC] Cannot find timing check

DSM_201302.SDF, 4836

module: DFFRXL, "instance: testbench.dsm_201302_inst.Out_offset_reg_0_"

SDF Warning: Cannot find timing check $recovery(posedge RN,posedge CK,...)

Warning-[SDFCOM_CFTC] Cannot find timing check

DSM_201302.SDF, 4858

module: DFFSRHQX1, "instance: testbench.dsm_201302_inst.K_out_reg_1_"

SDF Warning: Cannot find timing check $recovery(posedge SN,posedge CK,...)

All future warnings not reported; use +sdfverbose to report them.

Warning-[SDFCOM_CFTC] Cannot find timing check

DSM_201302.SDF, 4860

module: DFFSRHQX1, "instance: testbench.dsm_201302_inst.K_out_reg_1_"

SDF Warning: Cannot find timing check $recovery(posedge RN,posedge CK,...)

Total errors: 0

Total warnings: 105

***SDF annotation completed: Sat Dec 21 15:23:05 2013

Starting vcs inline pass...

478 modules and 17 UDPs read.

However, due to incremental compilation, no re-compilation is necessary.

ld -r -m elf_i386 -o pre_vcsobj_1_1.o --whole-archive pre_vcsobj_1_1.a --no-whole-archive

ld -r -m elf_i386 -o pre_vcsobj_1_2.o --whole-archive pre_vcsobj_1_2.a --no-whole-archive

if [ -x ../simv ]; then chmod -x ../simv; fi

g++-o ../simv -melf_i386-Wl,-whole-archive-Wl,-no-whole-archiveSIM_l.o 5NrI_d.o 5NrIB_d.opre_vcsobj_1_1.o pre_vcsobj_1_2.ormapats_mop.o rmapats.o/home/tian/programs/synopsys/vcs/linux/lib/libvirsim.so /home/tian/programs/synopsys/vcs/linux/lib/librterrorinf.so /home/tian/programs/synopsys/vcs/linux/lib/libsnpsmalloc.so /home/tian/programs/verdi/share/PLI/vcs/LINUX/pli.a/home/tian/programs/synopsys/vcs/linux/lib/libvcsnew.so /home/tian/programs/synopsys/vcs/linux/lib/libuclinative.so/home/tian/programs/synopsys/vcs/linux/lib/vcs_save_restore_new.o /home/tian/programs/synopsys/vcs/linux/lib/ctype-stubs_32.a -ldl -lm-lc -lpthread -ldl

../simv up to date

Chronologic VCS simulator copyright 1991-2011

Contains Synopsys proprietary information.

Compiler version E-2011.03; Runtime version E-2011.03;Dec 21 15:23 2013

Doing SDF annotation ...... Done

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.K_out_reg_2_

$hold( posedge RN:882, posedge SN:1369, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.P_reg_2_

$hold( posedge RN:882, posedge SN:1370, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.P_reg_3_

$hold( posedge RN:885, posedge SN:1374, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.K_out_reg_3_

$hold( posedge RN:885, posedge SN:1374, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.K_out_reg_0_

$hold( posedge RN:777, posedge SN:1376, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.P_reg_0_

$hold( posedge RN:777, posedge SN:1376, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.K_out_reg_5_

$hold( posedge RN:885, posedge SN:1392, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.P_reg_5_

$hold( posedge RN:885, posedge SN:1393, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.P_reg_4_

$hold( posedge RN:901, posedge SN:1400, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.K_out_reg_4_

$hold( posedge RN:901, posedge SN:1401, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.K_out_reg_1_

$hold( posedge RN:880, posedge SN:1404, limit: 1000 );

"csm18ic.v", 9109: Timing violation in testbench.dsm_201302_inst.P_reg_1_

$hold( posedge RN:880, posedge SN:1406, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.K_out_reg_0_

$hold( posedge SN:80505, posedge RN:80777, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.P_reg_0_

$hold( posedge SN:80505, posedge RN:80777, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.K_out_reg_1_

$hold( posedge SN:80539, posedge RN:80880, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.P_reg_1_

$hold( posedge SN:80541, posedge RN:80880, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.P_reg_2_

$hold( posedge SN:80495, posedge RN:80882, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.K_out_reg_2_

$hold( posedge SN:80494, posedge RN:80882, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.P_reg_3_

$hold( posedge SN:80471, posedge RN:80885, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.K_out_reg_3_

$hold( posedge SN:80471, posedge RN:80885, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.P_reg_4_

$hold( posedge SN:80503, posedge RN:80901, limit: 1000 );

"csm18ic.v", 9110: Timing violation in testbench.dsm_201302_inst.K_out_reg_4_

$hold( posedge SN:80504, posedge RN:80901, limit: 1000 );

经检查,所有出现violation的均为output端口,不知道是不是因为有些delay没加进去引起的还是确实是约束有问题?

请问你这个问题解决了吗我现在遇到了同样的问题,求解答

两个建议:1、把reset时间加长;

2、把sdf用PT处理一下,再用PT输出sdf做后仿

我也出现这样的问题我在modelsim仿真是通过的VCS就一直卡在那波形就全是黄色的

先解决hold timing问题吧,

遇到了同样的问题,请问小编是怎么解决的?

二楼说的对

小编问题解决了吗?同遇到这个问题,求解

louzhu小编 解决了吗? 我也遇到这样的问题了

这个贴又被挖出来了。见6楼,如果还有问题,那么可能需要修timing了

mark. Maybe will help.

请教一下小编,该Warning-[SDFCOM_CFTC] Cannot find timing check

DSM_201302.SDF, 4860

module: DFFSRHQX1, "instance: testbench.dsm_201302_inst.K_out_reg_1_"

SDF Warning: Cannot find timing check $recovery(posedge RN,posedge CK,...)

您是如何解决掉的?