pt报告同一条路径时delay type选择max和min分析的delay问题

时间:10-02

整理:3721RD

点击:

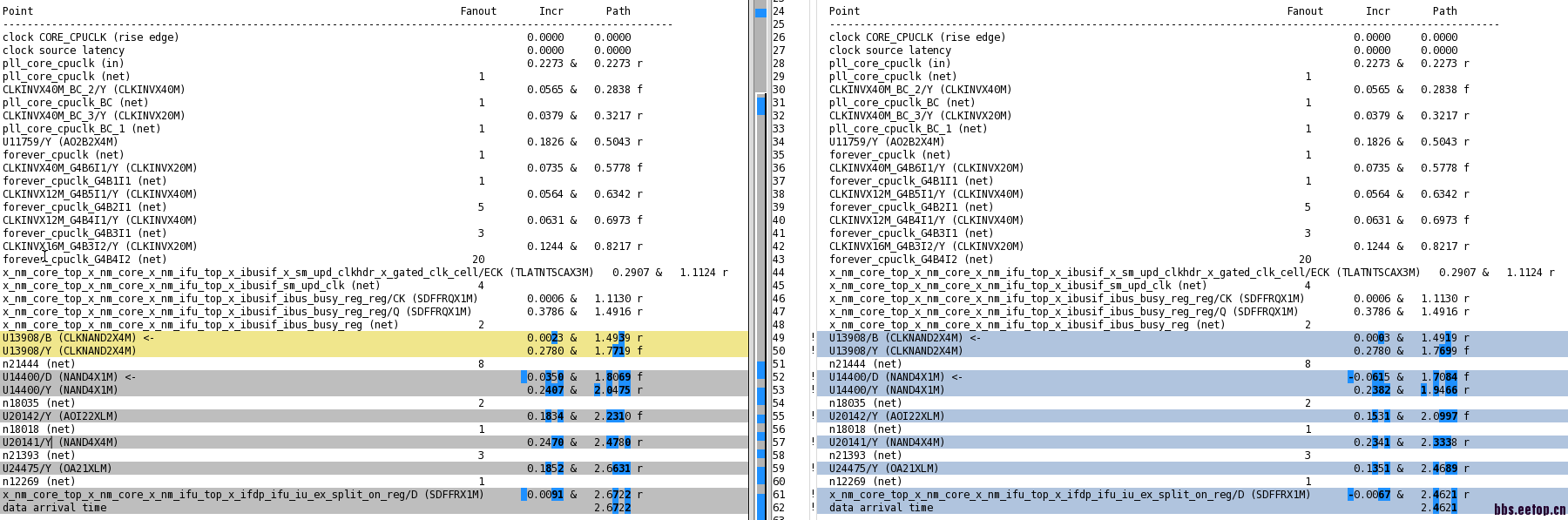

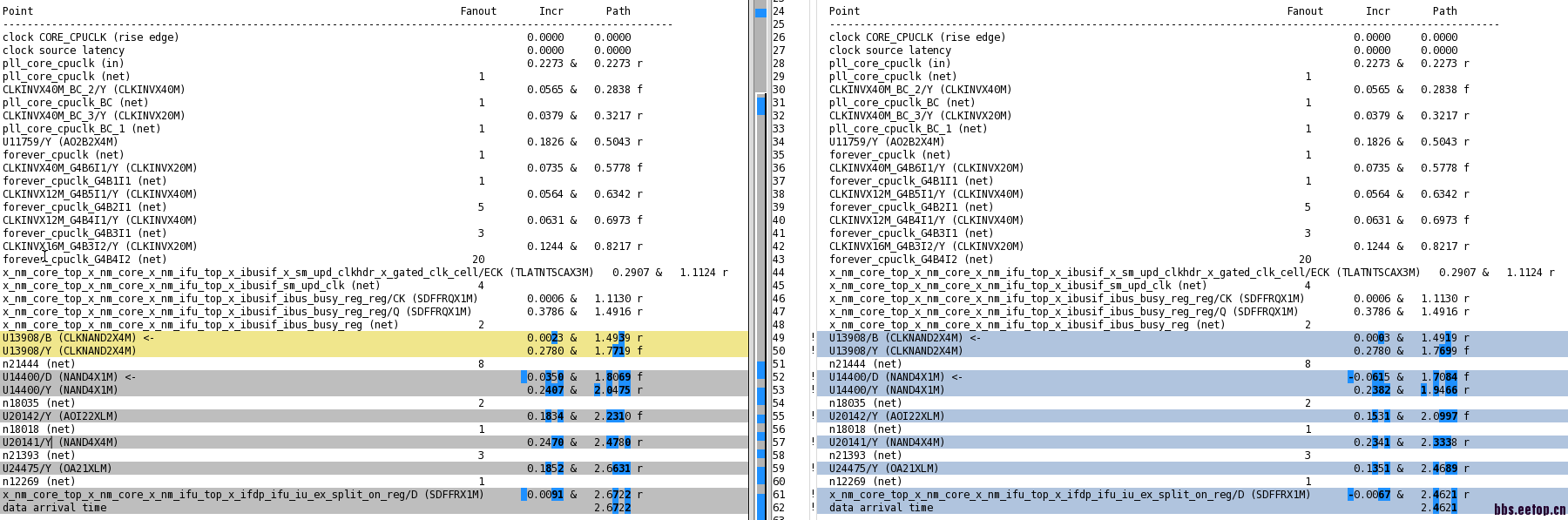

pt导入的是同一个verilog netlist,同一个spef,同一个lib。

我用pt报告同一条path,不同的delay type,分析出来的net delay和cell delay都不一样,请问这样是合理的么?

这里说的同一条path,是完全相同的一条了。途中经过的cell和net都是一样的。

贴一下我报出来的path的report吧。

我用pt报告同一条path,不同的delay type,分析出来的net delay和cell delay都不一样,请问这样是合理的么?

这里说的同一条path,是完全相同的一条了。途中经过的cell和net都是一样的。

贴一下我报出来的path的report吧。

当然有可能了, -max的时候是计算setup critical case, -hold是计算min delay case

如果还有疑惑请report_delay_calculation

setup计算的时候是max delay,hold计算的时候是min delay吧

通过report_delay_calculation确实看一个一个cell的timing arcs在max和min的情况下delay是不一样的。

但是我一直理解的cell delay是受到input端的transition和output 端的load来影响的。

那么如果max和min的delay_type可以report出不同的timing delay,就意味着一个cell的input transition和output load在这两个delay type是不同的。

感觉有点奇怪吧。毕竟path都是同一条的path,路径上的cell和net都一样,不知道为什么会计算出不同的数据。

回复 4# AveryYoung [/blib中]setup和hold都有相应的table

你一条path会有merge point,两个信号过来会有不同的slew.比如与非门的两个pin进来的slew可能是不一样的

遇到了同样的疑问,请问小编解决问题了吗?能否分享一下?