请问set_clock_latency 设太大会有什么不好

请问set_clock_latency 设太大会有什么不好,除了需要多加buffer和面积变大之外,还有什么不好的影响吗?

set_clock_latency 是指时钟源到寄存器的CK端的delay吧。

那么set_clock_lentcy 是不是一定要大于 set_clock_skew。

还有设置set_clock_skew有没有经验值啊,如何设置?

还有 set_clock_uncertainty一般是不是设置为clock的半个周期啊?

综合时设得差不多就行了,也没有多大意义,以为是ideal 。

可以让后端做一次CTS,估计个latency,

PR时感觉一般情况下不用设latency,因为clock tree 做好后自然会去计算实际的delay

set_clock_latency 是指时钟源到寄存器的CK端的delay吧。设太大会有什么不好,除了需要多加buffer和面积变大之外,还有什么不好的影响吗?

set_clock_lentcy 是不是一定要大于 set_clock_skew。

还有设置set_clock_skew有没有经验值啊

set_clock_uncertainty一般是不是设置为clock的半个周期啊?

latency无所谓的,skew比较重要

OCV的时候,latency太长,会有潜在问题。

lantency一般不要设计得太大,一般根据clock树上的leaf的数量而定,如果比较多,那么值就大一点,如果比较少就少设点,lantency一般跟时钟树的深度有关,值越大树的深度就越深.

所指潜在问题是什么

个人认为综合时latency可以不用设,不要让DC给clock加buffer,把clock当成是ideal的,布局布线时做CTS就会自动加buffer的,一般情况够用了。

skew比较重要,经验值我也想知道我一般设的比较小~

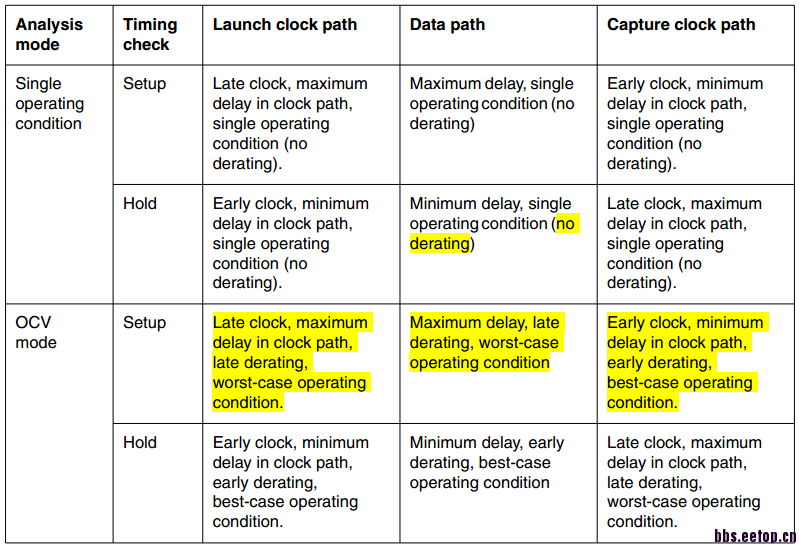

OCV是指在capture 和 launch两条时钟路径上采用两种CORNER去分析,时钟路径越长两种coner分析的偏差值就越大越容易出现slack.

If timing of design is marginal, the design might not be convergent, which causes run timing very long.

All additional buffering will increase the power consumption and you might have difficult time to fix hold time issue. Remember hold time is more important than setup time.

在综合阶段

clock uncertainty = clock skew + jitter + margin

综合的时候如无特殊要求可以不用加set_clock_latency,除非已经确定要用useful_skew,比如memory时钟端。

后端CTS的时候可以设置max insertion delay控制latency,太长会增加功耗和面积,也可能会引起hold违例,具体数值视时钟树深度来定。

好高深啊,我需要逐个消化,谢谢楼上诸位

那么set_clock_uncertainty一般是不是设置为clock的半个周期啊?

或者如何设置啊,还有clock skew , jitter , margin 如何设啊

个人认为同步情况下设置 set_clock_uncertainty没有

看完了还是不知道uncertainty这个值设多少,怎么没有人说说经验值啊

请问你知道了吗?我也想知道,如果知道可以告诉我吗?谢谢诶,急需。

不同的工艺库不一样,当然还取决于你的时钟质量,可以给你一个参考,90nm: 120ps setup, 90ps hold.

这样看来,set_clock_latency在一般情况下,综合时不会对路径其约束作用,因为时钟是理想的。在PR过程中,PR会自动根据布时钟树,布出来的时钟延迟才是最终的结果,跟之前在DC中的set_clock_latency设置就没什么关系了。听听不同的意见。

set_clock_skew

Note: This command is obsolete starting in 2006.06. It has been replaced by

set_clock_latency, set_clock_uncertainty and set_propagated_clock commands. Please

adjust your script accordingly.

set_clock_uncertainty半个周期也太夸张了。一般根据时钟源来设

我们用TSMC018工艺clock_uncertainty经验值应该是setup 1ns,hole 0.5ns

值有点大吧

skew 比较重要

40g的好像是150ps

对的,OCV的时候,launch clock 和capture clock 计算的时候可能用不同的系数,slew如果你insertion delay做的太长,skew会比较大,timing不好收敛。

我们在28工艺一般设10%

uncertainty的值不是jitter+skew吗?